# Analog Electric Circuits Synthesis using a Genetic Algorithm Approach

Walid Mohamed Aly

College of Computing and Information Technology

Arab Academy for science, Technology and Maritime Transport

Alexandria, Egypt

#### **ABSTRACT**

Evolvable hardware is a hardware that depends on evolutionary algorithms (EAs) for performing electrical circuit synthesis and evolving its electrical circuit architecture, furthermore it depends on EAs for making the necessary adaptations to this architecture while working on line.

This paper presents a new approach for solving the electrical circuit synthesis problem using genetic algorithms as an automated design technique, the proposed approach offers a new coding style for the chromosome representing the electric circuit, and also minimizes the chromosome size in an attempt to solve the scalability problem associated with evolvable hardware. This approach is tested upon the synthesis of low pass electrical filter and has proved to be efficient and capable of handling more complex circuit design tasks with minor future changes.

#### **Keywords**

Automated design, Artificial Intelligence, electric circuit synthesis, Genetic algorithms.

#### 1. INTRODUCTION

Evolutionary algorithms (EAs) are algorithms that attempt to solve real life computation problems using a technique based on an analogy with the way nature evolves its individuals. Using EAs, the candidate solution to the problem under investigation is coded as a chromosome genetic structure and different gene like operators are applied until a satisfactory solution is reached [1].

Evolvable Hardware (EHW) is a relatively new term which found its way through since the early 1990s. EHW refers to hardware that has its electric circuit architecture (including its topology and different values of embedded components) chosen by an EA. Furthermore, if while working online a change has occurred in the operating condition that would prevent the hardware from performing its task, a system depending on EHW can change its architecture autonomously. This feature gives the hardware the privilege of being self maintainable, if a certain fault occurred in a circuit component, EHW would change its hardware architecture to adopt with this fault and continue working efficiently [2]. There are two kinds of EHW [3]: Extrinsic EHW in which a software simulation is used to evaluate the candidate solutions and only the best one will be implemented in hardware and Intrinsic EHW in which every chromosome during evolution process will cause the hardware to be actually reconfigured in order to evaluate it. Both extrinsic and intrinsic evolvable hardware have to face the scalability problem. The scalability problem can be divided into two problems [2]:-

- i- The scalability of the chromosome representing the electric circuit.

- ii- The scalability of the mathematical computations required for evolving the solution, this is a much important problem than the first one as an EHW experiment can run for days [4].

### 2. CIRCUIT SYNTHESIS USING EVOLUTIONARY ALGORITHMS

#### 2.1 Definition of Electric Circuit Synthesis

One of the definitions of electric circuit synthesis is designing the topology of an electrical circuit with a fixed set of electrical components, this set might contain two terminal elements like resistances, inductances, capacitances, or three terminal elements like transistors or other electrical functional units. Besides finding the best topology, electrical circuit synthesis aims to find the exact values of these electrical components to achieve a certain performance.

#### 2.2 Selected Previous EA Circuit Synthesis Work

Electric circuit synthesis is a creative work that has always been well-known to need a creative intelligent human being to accomplish it. The search space for this problem is outsized enough that this problem was tackled by many heuristic and meta-heuristic approaches including of course the EAs.

Koza et al. [5] presented a single uniform approach for the automatic synthesis of eight different analog electrical circuits using genetic programming, in designing an electrical circuit, genetic programming starts with an embryo circuit and develops a small program which controls the addition of different components to the electrical circuit, this method ensures that there are no evolving of restricted topologies. The results were promising enough that the authors declared "....the general applicability of Genetic Programming (GP) for solving the problem of automatic synthesis of analog electrical circuit".

An automated circuit design system for the evolution of CMOS amplifiers is introduced in [6]. The authors believed that with some effort, novice circuit designers will invent basic analogue circuits.

In [7], the authors proposes parallel and recursive decomposition strategy as a new decomposition strategy to accelerate the adaptation process from methodology perspective, the authors use the proposed strategy on Xilinx Virtex-II Pro (XC2VP20) FPGA to evolve adaptive combinational logic circuits.

#### 2.3 Main advantages of EA circuit synthesis

Before recognizing EHW, there had been always conventional techniques that were sufficient to perform the task of circuit synthesis, however there are three main advantages of EA circuit synthesis that can be summarized as follows:

1. According to the famous 1960's Moore's law[8], the number of electronic components in an electronic chip will double every 18 month, if this law continues to be effective, then by the end of next decade we will reach the size of trillion components this will make it impossible for a human to design the electric circuits[9].

In spite of this size complexity fact and as Koza stated: "There has been no general automated technique for synthesizing an analog electrical circuit from a high level statement of the behavior of the circuit"[5]. EHW might be the solution for this problem.

- Since EHW depends on new techniques for evolving the circuit design, EHW can evolve electrical circuit structures that would never be discovered by human designers.

- 3. EHW is a sub branch of EAs, that relation makes EHW shares the same advantages of EAs and most remarkably, the ability to solve a problem with very little prior knowledge about it. Abstraction of number of inputs and outputs and the required relation between them might be enough for EHW to perform its task.

## 3. EVOLUTION OF ANALOG ELECTRONIC CIRCUITS USING GENETIC ALGORITHM

This paper presents a new approach for solving the electrical circuit synthesis problem using genetic algorithm aided by developing a new coding for the chromosome that will enable genetic algorithm to solve the problem of finding both the topology and exact values for the different electrical components embedded in the circuit.

#### 3.1 Basic Electric Circuit

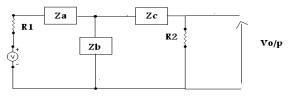

The basic electric circuit that will be used in evolving the electrical circuit is as shown in figure 1. Choosing the basic circuit is hypothetical, although it seems from the figure the electric circuit topology is fixed, our coding will enable the evolution of different circuit topologies, and gives the evolutionary process its freedom to choose.

Fig 1: Basic Electric Circuit

#### 3.2 Electric Circuit Coding

Each electric circuit is coded as a chromosome with genes that take real values as shown in figure 2.

Fig 2: Electrical circuit coding as a chromosome

Our basic circuit has three impedances, each impedance will be described in the chromosome using four genes as shown in figure 3:-

| r | 1 | c | Mode |

|---|---|---|------|

Fig 2: Impedance Coding

The value of the mode gene will range from 1 to 18, mode values 17, 18 are the special values. Mode 17 means open circuit impedance and mode 18 means short circuited impedance. According to the value of the Mode bit, the connection topology of the resistance, inductance and capacitance of the impedance is determined.

r, l and c are real numbers that range between zero and one and are used to evaluate the actual values of the impedance components according to the following equations:

$$R = R_{\min} + r * (R_{\max} - R_{\min})$$

(1)

$$L = L_{\min} + l * (L_{\max} - L_{\min})$$

(2)

$$C = C_{\min} + c * (C_{\max} - C_{\min})$$

(3)

Where  $R_{min}$ ,  $L_{min}$  and  $C_{min}$  represent the minimum values that the resistance, inductance and capacitance can have respectively and  $R_{max}$ ,  $L_{max}$  and  $C_{max}$  represent the maximum values that they can have, these values are problem dependent and require basic knowledge about the problem under consideration. The last two genes in the chromosome will represent the values of the two resistances in our circuit (R1 and R2).

With the presented method for coding, the complexity of the length of the chromosome for an n number of components is O(n), this approach minimizes the chromosome size in an attempt to solve the scalability problem associated with evolvable hardware. The chromosome structure stores the values of components and mode of connections but does not store all the steps of connection.

**Coding Restrictions:** All the circuit impedances can have the modes from 1 to 16, only  $Z_b$  can have mode 17 but cannot have mode 18,  $Z_a$  and/or  $Z_c$  can have mode 18 but cannot have mode 17. Table 1 shows the electrical diagram that represents the value of each mode.

#### 3.3 Fitness Calculation

Each chromosome in the generation represents a certain electrical circuit with its own topology and set of values, fitness calculation involves decoding the chromosome to the equivalent electric circuit it represents and calculating its estimated transfer function  $T_{\rm e}$ , the transfer function is problem specific, for example in this paper, the interest is in solving the filter design problem,  $T_{\rm e}$  will be the ratio between the output voltage and input voltage at different applied frequencies.

$$T_e(f) = \frac{V_o}{V_i} \tag{4}$$

$V_{\rm i}$  is applied as a constant amplitude voltage to the filter with a variable frequency that spans the frequency range of interest to the filter application,  $V_{\rm o}$  is the corresponding output voltage. The exact optimum Transfer Function response T of the filter is known from the problem specification.

The evaluation Fitness criterion considered is:-

$$Fitness = \left(1 - \frac{Var(T - T_e)}{Var(T)}\right) * 100 \tag{5}$$

Where  $T_e$  is the estimated model transfer function. The higher the fitness, the better the performance of the evolved electrical circuit, taking into consideration that the fitness value of the chromosome that represent the electric circuit is a real number that varies between zero for worst performance and one hundred for best performance.

#### 4. CASE STUDY

#### 4.1 Problem Description

The problem used to test our GA approach for electrical circuit synthesis is the design of an ideal low pass filter whose ideal characteristics is to have an exact cut off frequency at 100 Hz. The operating frequency range of the filter is from 0 Hz to 1000 Hz. The filter design will be composed only from passive electrical elements, the range of values for these elements are based on the choice made in [10] and are as listed in table 2:

Table 1. Minimum and Maximum Values for Circuit Elements.

| R <sub>min</sub> | 1 Ω     |

|------------------|---------|

| R <sub>max</sub> | 100 K Ω |

| $L_{\min}$       | 0.1 mh  |

| $L_{max}$        | 1.5 h   |

| $C_{\min}$       | 10 pf   |

| $C_{max}$        | 200 ηf  |

This problem is chosen to demonstrate the performance of the algorithm for the following reasons:-

- 1. The real world is analog by nature and even the digital circuits use analog circuits as an interface.

- Most of the efforts towards automating the design of circuits are directed towards the digital circuits, a lot of effort can still be done in analog design field.

- 3. The passive analog filter is simple in structure as it contains only two-terminal devices, so it looks like a simple test that the algorithm should pass .Filter design is a totally well understood discipline that a comparison of results can easily be done even with a simple look at curves.

Table 2. Equivalent Electric Diagrams for each mode.

| Mode | Electric Diagram    | Mode | Electric Diagram |

|------|---------------------|------|------------------|

| 1    | R<br>               | 10   | R L C            |

| 2    | <b>-∿88</b> &−<br>T | 11   | L R              |

| 3    | c<br>-              | 12   | R C L            |

| 4    | R L C               | 13   |                  |

| 5    | L<br>C<br>C         | 14   | L<br>L           |

| 6 | R L     | 15 | C |

|---|---------|----|---|

| 7 | R C     | 16 |   |

| 8 |         | 17 |   |

| 9 | R L C C | 18 | • |

#### **4.2 GA Parameters**

Table 3 represents the main parameters used in applying GA.

**Table 3. GA Parameters**

| Selection Method              | Stochastic universal sampling |

|-------------------------------|-------------------------------|

| Coding Type                   | Real Values                   |

| Cross Over Rate               | 0.7                           |

| Mutation Rate                 | 0.01                          |

| Number of individuals         | 40                            |

| Maximum number of generations | 40                            |

#### 4.3 Results

- The best fitness achieved was equal to: 90.362 and was found at generation 36.

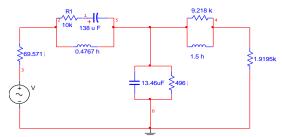

- The equivalent electrical circuit of that chromosome is as shown in figure 4.

- This best fitness is in respective to the chromosome structure shown in figure 5.

Fig 4: Evolved Filter.

| 1 | 0.31791 | 0.6022 | 12 | 0.07100 | 1 | 0.24771 | 1// | 0.040526 | 0.22473 | 0.0673 | 15 | 0.10197 | 0.0068578 |

|---|---------|--------|----|---------|---|---------|-----|----------|---------|--------|----|---------|-----------|

| 1 | 0.31701 | 0.0322 | 12 | 0.52100 | 1 | 0.24771 | 14  | 0.043320 | 0.22413 | 0.0013 | 12 | 0.15107 | 0.0000370 |

|   |         |        |    |         |   |         |     |          |         |        |    |         |           |

Fig.5: Filter Chromosome Structure

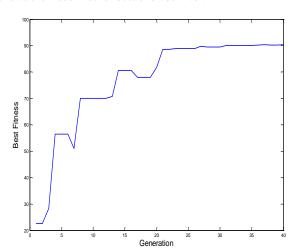

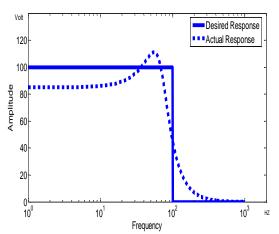

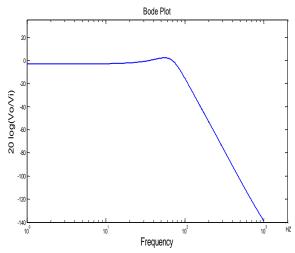

Figure 6 shows the progress of the algorithm (Best Fitness against Generation index). Figures 7 shows a comparison between the characteristic of the ideal low pass filter and the characteristics of the actual filter achieved by GA. Figure 8 shows the Bode Plot for best evolved filter.

Fig 6: Best Fitness vs. Generation.

Fig 7: Desired & Actual Responses (Semi Log Scale).

Fig 8: Bode Plot for best Evolved Filter.

#### 4.4 Discussion

The proposed extrinsic evolvable hardware approach proved its efficiency by evolving a reasonably efficient design of the required low pass filter by the 36 generation.

The reason there exist a gap error between the desired and actual responses around the cutoff frequency is that the response of an ideal filter is used as the desired response. An ideal low pass filter eliminates all frequencies above the cutoff frequency while passing those below unaltered; an ideal low pass filter can be realized theoretically but is not realizable for practical real signals. This optimum filter response is used as the desired response to force GA to find a filter as near as possible in performance to the ideal filter.

#### 5. CONCLUSION

A new approach for designing electrical circuits using a metaheuristic approach was proposed, this approach was tested on designing the standard low pass electrical filter. This approach is simple yet promising to be applied successfully with minor changes to more complicated electrical circuit designs.

The relatively simple structure of our chromosome that represents the circuit and the modest computation requirements imply that EA might play a key role in electric circuit synthesis within the next decades.

The future work could be building upon this simple technique to make it capable of handling three terminal devices like transistors, and also adding the possibility of a multistage circuit evolved, so far it is only a single stage circuit that the proposed algorithm can evolve.

#### 6. REFERENCES

- [1] Guzek, M.; Bouvry, P.; Talbi, E.-G., "A Survey of Evolutionary Computation for Resource Management of Processing in Cloud Computing [Review Article]," IEEE Computational Intelligence Magazine, vol.10, no.2, pp.53,67, 2015.

- [2] Mrazek, V.; Vasicek, Z., "Acceleration of transistor-level evolution using Xilinx Zynq Platform," Evolvable Systems (ICES), 2014 IEEE International Conference on, vol., no., pp.9,16, 9-12 Dec. 2014

- [3] Walker, J.A.; Trefzer, M.A.; Bale, S.J.; Tyrrell, A.M., "PAnDA: A Reconfigurable Architecture that Adapts to Physical Substrate Variations, *IEEE Transactions* on Computers, vol.62, no.8, pp.1584-1596, Aug. 2013

- [4] Wang Nantian; Qian Yanling; Li Yue; Zhuo Qingqi; Li Tingpeng, "Survey on evolvable hardware and embryonic hardware, 2013 IEEE 11<sup>th</sup> International Conference on Electronic Measurement & Instruments (ICEMI), vol.2, pp.1021-1026, 16-19 Aug. 2013.

- [5] Mrazek, V.; Vasicek, Z., "Acceleration of transistor-level evolution using Xilinx Zynq Platform,", IEEE International Conference on Evolvable Systems (ICES), pp.9,16, 9-12 Dec. 2014

- [6] Cristian Ferent and Alex Doboli. Novel circuit topology synthesis method using circuit feature mining and symbolic comparison. In Proceedings of the conference on Design, Automation & Test in Europe (DATE '14). European Design and Automation Association, 3001 Leuven, Belgium, Belgium, 2014.

- [7] Z. Jixiang; L. Yuanxiang and Z. Wei. Adaptive combinational logic circuits based on intrinsic Evolvable Hardware. In proceedings of IEEE Congress on Evolutionary Computation: pp 18-21, 2009

- [8] G. Moore. Cramming more Components onto Integrated Circuits. Electronics, 38(8): pp.114-117, 1965.

- [9] Serra, H.; Santos-Tavares, R.; Paulino, N., "A top-down optimization methodology for SC filter circuit design,", 2014 IEEE International Symposium on Circuits and Systems (ISCAS), vol., no., pp.1672,1675, 1-5 June 2014

- [10] J. Lohn and S. Colombano. Circuit Synthesis using a Linear Representation. In proceedings of the second Int'l Conf on Evolvable Systems: From Biology to Hardware, Berlin, Springer-Verlag: pp 125-133, 1998

$IJCA^{TM}$ : www.ijcaonline.org