# Design and Implementation of an Efficient 4G Digital down Converter used in Wireless Receiver Systems

Shrita G, A.R Aswatha, PhD

Department of Telecommunication,

Dayananda Sagar College of Engineering, Bangalore,

Affiliated to Visvesvaraya Technological University, Belagavi, India

#### **ABSTRACT**

A Digital Down Converter (DDC), which is basically used to convert an intermediate frequency (IF) signal to its baseband form, forms an integral part of wireless receivers. The major functional blocks of a DDC constitute a mixer, Numerically Controlled Oscillator (NCO) and an FIR filter chain. In this paper, an area efficient and high speed DDC has been designed and implemented. On comparison of the results with that of the existing methodology, the designed architecture achieves 44.8% area efficiency and 80.7% improvement in speed.

# **Keywords**

DDC, folded, unfolded, filter chain, area, speed

#### 1. INTRODUCTION

Communication is mainly classified into wired and wireless. The invention of wireless communication has been a boon to mankind. Information can now be transmitted from one place to another, without the use of a physical electrical medium. With the advances in wireless technology, information can be transmitted through a distance of few meters (Ex: Television remote control) to thousands of kilometers (Ex: Radio communication). This would indeed come at the cost of onchip area, speed and power where a lot of research is being carried out to optimize the same [1],[2],[3].

The wireless communication technology has evolved from the first generation (1G), which marks the beginning of the mobile cellular era; through the second and third generations (2G, 3G), where technologies such as GPRS, EDGE, GPS, GSM, video conferencing emerged; and now, to the fourth generation (4G), which provides advanced services such as IP telephony, cloud computing, high-definition mobile TV, etc.

When a signal is being transmitted over a wireless medium, it may be affected by Inter-Symbol Interference (ISI) which causes the signal to distort. In order to avoid this, signal scaling is performed. At the transmitter side, the signal is up scaled from baseband to intermediate frequency (IF) signal and transmitted. On the receiver side, the signal is transformed back from IF to baseband frequency. This down scaling operation is performed by a DDC.

In this paper, an efficient 4G Digital Down Converter has been designed and implemented. Simulation is performed in MATLAB to verify the functionality of the design [4]. The design is then developed in VERILOG Hardware Description Language, simulated using the ModelSim simulator and then synthesized using the Xilinx Project Navigator.

The design of the filter chain forms an intricate part of the DDC in reducing the sampling rate and in performing low pass filtering to obtain the actual baseband spectrum [5]. The two widely known filters that can be used to design the filter chain are: the Finite Impulse Response (FIR) filter and the Infinite Impulse Response (IIR) filter. The IIR filters do not provide linear phase response and are not stable, since they are recursive in nature. They consume more power. On the other hand, the FIR filters, developed by Parks McClellan, are stable in nature, non-recursive and consume low power. They provide optimal filter coefficients using an indirect method. They provide linear phase response which implies that they have symmetrical coefficients. They are more suited for baseband, anti-aliasing and low pass filtering operations. Due to these advantages, FIR filters are used to design the filter chain of the DDC.

# 2. ARCHITECTURAL BLOCK DIAGRAM OF DIGITAL DOWN CONVERTER

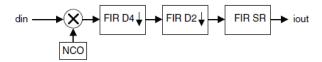

A block diagram of the DDC is shown in Fig. 1. The major functional blocks constitute a mixer, an NCO and a filter chain [3]. Firstly, the received input signal is multiplied with the IF sine signal from the NCO. The output of the mixer is then processed through the filter chain, which performs low pass filtering to obtain the original baseband signal.

Fig. 1: Architectural block diagram of DDC

#### 2.1 Design of NCO

The Numerically Controlled Oscillator has been implemented using the widely used, Look-up Table (LUT) approach. The NCO produces a cosine signal having IF frequency. The mixer, upon mixing this signal with the received input signal, produces the baseband frequency signal, which is then fed to the filter chain

#### 2.2 Design of Filter Chain

The filter chain consists of three levels of filtering [3]. The first stage consists of a 35 tap FIR filter, followed by decimation by a factor of 4 (denoted as D4 in Fig. 1). The transition band for this filter is wide, i.e., it is not sharp. The second stage consists of a 63 tap filter, followed by decimation by a factor of 2 (denoted as D2 in Fig. 1). The transition band for this filter is moderate. The last stage

contains a single rate 111 tap filter which provides a sharp transition band. The decimators are used to reduce the sampling rate.

## 3. FIR FILTER ARCHITECTURE

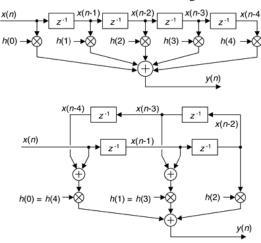

Let us consider an FIR filter with S filter taps. The existing architecture would require S number of multipliers to implement such a filter. This general purpose architecture is known as the "unfolded filter architecture". The proposed architecture, on the other hand, makes use of the symmetric property of the filter coefficients and provides a way to reduce the number of multipliers used. Thus, in a general case of an FIR filter with symmetrical coefficients, the number of multipliers required reduces to S/2, if S is even or ((S-1)/2) +1, if S is odd. This type of filter design is called the "folded filter architecture" [4]. An example of a 5 tap unfolded and folded FIR filter structure is as shown in Fig. 2.

Fig. 2: Unfolded and Folded FIR structure

In this example, S=5 multipliers are needed in the unfolded architecture, whereas only (S-1/2)+1=3 are needed for the folded. Multipliers are the ones that consume majority of the power and space. Each multiplier consists of around 200 full-adders. Thus, the unfolded architecture would require 5\*200=1000 full-adders, while the folded architecture would just require 3\*200=600 full-adders. This implies that the unfolded architecture has huge area requirement. The larger the on-chip area, the higher the power consumed. The folded architecture provides a way to reduce this area requirement by a significant amount. Lesser the area required, better the speed and lesser the power consumed.

#### 4. IMPLEMENTATION

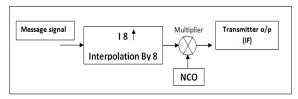

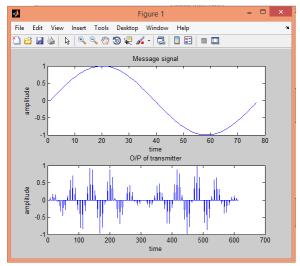

The transmitter has been implemented as shown in Fig. 3. A message signal having frequency (fm) of 150KHz and sampling frequency (fs) of 11.2MHz is up scaled by performing interpolation. The interpolated signal is then mixed with the output of an NCO having carrier frequency (fc) of 1.5MHz and sampling frequency of 92MHz. The resulting signal is the IF signal which is transmitted.

Fig. 3: Block diagram of transmitter

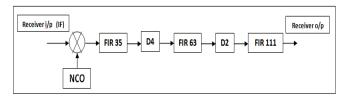

At the receiver side, the block diagram of the DDC that has been implemented is as shown in Fig. 4. The received IF signal is multiplied with the NCO output, and then the resulting signal is made to pass through the filter chain. The signal is passed through a 35 tap FIR filter, followed by decimation process by a rate 4. Next the signal is filtered by a 63 tap FIR filter, followed by decimation process by a rate 2. The resulting signal is then filtered by a 111 tap FIR filter to obtain the receiver's output.

Fig. 4: Architectural block diagram of DDC at the receiver

The NCO has been implemented using the LUT approach. The filter chain has been implemented using both, the existing unfolded architecture and the proposed, folded architecture. The unfolded architecture makes use of a total number of 219 multipliers, which implies 219 \* 200 = 43800 full adders. Whereas the folded architecture uses only 106 multipliers, i.e. 106 \* 200 = 21200 full adders. This shows that the folded FIR architecture achieves reduction in area required by a significant amount.

#### 5. SIMULATION AND RESULTS

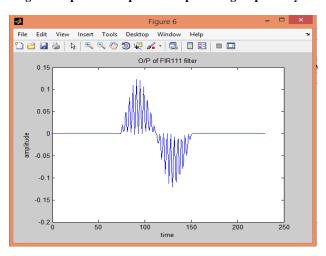

The simulation of the DDC is performed in MATLAB to verify its functionality. The message signal considered at the transmitter and the IF signal to be transmitted, obtained by multiplying the interpolated message signal and the output of NCO are as shown in Fig. 5. The different stages of filtering: 35 tap, 63 tap and 111 tap, can be observed in Fig. 6 and 7.

Fig. 6 shows the output of the first 2 stages of filtering, where the transition from pass band to stop band is wide in the first stage and improves to a moderate transition band in the second stage. A decimation operation is performed after each of these filtering operations to reduce the sampling rates. The output of the 35 tap filter is decimated by a factor of 4, i.e. every fourth sample is picked up and the rest are dropped. This decimated output is then fed into the 63 tap filtering stage, followed by decimation by a factor of 2.

Fig. 5: Messgae signal and output of transmitter respectively

4 Figure 3 Insert Tools Desktop Window 🖺 😅 🔒 🐚 | 🥾 | 🔍 🤏 🖑 🤚 🐙 🔏 - | 🛃 | 🔲 🔡 | 🖿 🛄 O/P of FIR35 filter 0.4 0.2 -0.2 -0.4 100 300 O/P of FIR63 filter 0.2 0 -0.1

Fig. 6: Output of 35 tap and 63 tap filtering respectively

Fig. 7: Output of 111 tap FIR filter

Fig. 7 shows the output of the last stage of filtering, where the sharp transition band is obtained. This is the output of the DDC. This signal upon demodulation produces the original message signal that was transmitted.

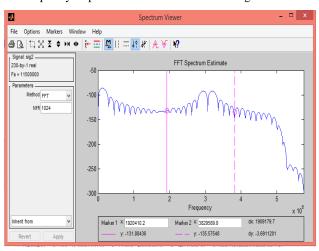

The frequency response obtained is as shown in Fig. 8.

Fig. 8: Frequency response

The design is then developed in VERILOG using the ModelSim simulator. Both the unfolded and folded architectures are implemented. Upon synthesizing the two implementations using Xilinx Project Navigator, the results are obtained as follows:

- Disk Utilization Details:

- ➤ Unfolded Architecture: Number of Slices: 55978 out of 2448 2286%

- Folded Architecture: Number of Slices: 25097 out of 2448 1025%

- Timing Details:

- Unfolded Architecture: Minimum period: 102.449ns (Maximum Frequency: 9.76MHz)

- Folded Architecture: Minimum period: 82.746ns (Maximum Frequency: 12.085MHz)

On comparison of the results, we can see that the folded FIR architecture provides better area efficiency and speed, compared to the existing architecture. The area requirement of folded architecture is less than that of the unfolded by 44.8%. The speed of the folded architecture is 80.7% more compared to the unfolded architecture.

# 6. CONCLUSION

An efficient 4G Digital Down Converter has been implemented using VERILOG Hardware Description Language. The filter chain of the DDC has been implemented using both, the existing architecture, i.e. unfolded and the proposed folded architecture. On comparison of the results, it is clearly seen that the folded architecture provides a significant improvement in terms of area efficiency and speed. The folded FIR architecture achieves reduction in area required by 44.8% and an increase in speed by 80.7% as compared to the unfolded architecture.

#### 7. REFERENCES

- [1] Huddar, S.R.; Rupanagudi, S.R.; Kalpana, M.; Mohan, S., "Novel high speed vedic mathematics multiplier using compressors," *Automation, Computing, Communication, Control and Compressed Sensing (iMac4s), 2013 International Multi-Conference on*, vol., no., pp.465,469, 22-23 March 2013

- [2] Sushma R. Huddar, Sudhir Rao Rupanagudi, Venkatesh Janardhan, Surabhi Mohan, and S. Sandya, "Area and Speed Efficient Arithmetic Logic Unit Design Using Ancient Vedic Mathematics on FPGA," in Advances in Computing, Communication, and Control, pp. 475-483, Springer, Berlin Heidelberg, 2013.

- [3] Huddar, S.R.; Rupanagudi, Ramya R.; Yadav S.; Jan S., "Novel Architecture for Inverse Mix Columns for AES using Ancient Vedic mathematics on FPGA," International Conference on advances in Computing, Communication and informatics (ICACCI). IEEE 2013.

- [4] Qingxiang Zhang and Xiaoxiao Su, "The Design of Digital Down Converter Based on FPGA", Sch. Of Electron. & Inf. Eng., Harbin Inst. Of Technol., Harbin, China, September 2009.

- [5] Mingxian Li, Lingyu Chen and Jiang Hong Shi, "Intermediate Frequency Design of Broadband Wireless Adhoc Network System", Dept. of Commun. Eng, Xiamen Univ., Xiamen, China, August 2009.

- [6] Lattice Semiconductor Corporation, "Multi-Channel Digital Up/Down Converter for WiMAX Systems", USA, April 2009.

- [7] Sundarajan V and Parhi KK, "Synthesis of low power folded programmable coefficient FIR digital filters", Dept. of Electr. And Comput. Eng, Minnesota Univ., Minneapolis, USA, June 2000.

## 8. AUTHORS BIOGRAPHY

#### Shrita G

Pursuing MTech degree in Digital Communication and Networking specialization, from Dayananda Sagar College of Engineering, Bangalore. Completed B.E. in the field of Electronics & Communication, from SJB Institute of Technology, Bangalore in 2012. Interest of research lies in

digital communication, wireless communication, cryptography and network security. Has published papers on Wireless Communication and Cryptography in International Journals. She has also presented papers in National Conferences.

#### Dr. A R Aswatha

Received B.E Degree from Mysore University in 1991, M.Tech Degree from M.I.T Manipal in 1996, M.S. Degree from B.I.T.S. Pilani in 2002, Ph.D degree in 2010 from Dr. M.G.R University. Currently he is working as Professor and Head of the Department of Telecommunication Engineering, Dayanand Sagar College of Engineering, Bangalore, India. His main research Interests include Analysis and design of Low Power VLSI Circuits, Embedded System Design and Image Processing.

IJCA™: www.ijcaonline.org