# Comparative Analysis of Universal Gates using MCML and CMOS Technique

Ginni Jain Research Scholar GITS, Udaipur Rajasthan, India Keerti Vyas Research Scholar GITS Udaipur Rajasthan, India

Rajeev Mathur professor GITS, Udaipur

#### ABSTRACT

MOS current mode logic (MCML) is an emerging logic family which is gaining attention due to its high speed of operation, robust performance and presence of mere switching noise as compared to the CMOS logic family. In this paper we have compared universal gates using MCML and conventional CMOS in terms of power and propagation delay at 16-nm Technology node. Comparative analysis shows that MCML universal gates has less power and delay as compared to conventional CMOS based universal gates at 16 nm technology. Variability analysis establishes MCML based universal gates as the most resilient and immune to various electrical parameters.

#### Keywords

MCML, CMOS, power and delay

## **1. INTRODUCTION**

The on-chip integration of various analog and digital circuits requires higher speed of operation with less power consumption. The conventional CMOS technology is not capable of providing an efficient solution to these requirements. The emerging class of MOS current mode logic (MCML) is proving to be a promising technology for the current trends of technology requirements due to its higher speed of operation. MOS implementation of current mode logic (CML) is preferred over bipolar CML because of scalability of its feature size and less power consumption with

higher speed of operation [1] [2] [3]. Moreover, CMOS logic family suffers from large dynamic power dissipation at high frequencies.

Nowadays, high-speed circuits use a well-known logic style, namely the current mode logic (CML) [4]. Designing highspeed circuits puts additional constraints on the design. For instance, circuits forming the blocks of a Giga-bit communication system should be simple and consist of a minimum number of active devices. Also, PMOS devices should not be used in high-speed signal processing circuits due to the fact that PMOS devices have less charge carrier mobility which makes them have an inferior unity-gain frequency with respect to NMOS devices. At high frequencies, CML circuits operate with lower supply voltages than CMOS circuits. Thus, CML circuits are a better choice for high speed applications.

In this paper, a more general approach is taken. Two-input MOS CML elementary logic gates (AND, OR, NAND and NOR) are investigated. The 16 nm technology is used.

Asst. Professor GITS, Udaipur Rajasthan,India

Vijendra K Maurya

#### 2. MOS CURRENT MODE LOGIC

Design and performance parameter of MCML logic are given in subsequent sections:

## 2.1 Power efficiency of MCML

The power consumed by an MCML gate is

$$P_{MCML} = I_{BIAS} X V_{DD}$$

(1)

Where,

P<sub>MCML</sub> - Power consumed by MCML gate

I<sub>BIAS</sub> – Bias current

V<sub>DD</sub> – Power supply

As per the above equation the power consumed by an MCML gate does not depend on the operating frequency. An MCML gate consumes constant current (and power) from the power supply network. This behavior is in contrast to the CV <sup>2</sup>f power dissipated by conventional CMOS, where the power consumed by a static CMOS gate exhibits a linear relationship with the operating frequency. MCML is therefore more power efficient at high frequencies as compared to static CMOS. MCML based universal gates are introduced in this paper to perform power and delay analysis between MCML and CMOS.

## 2.2 Delay

Delay is the time required for the output to reach 50% of its final output level when the input changes to 50% of its final input level.

## 2.3 Low noise environment of MCML

CMOS circuits suffer from simultaneous switching noise (SSN), which accounts for a major portion of the total on-chip noise. In contrast, the constant current of MCML significantly lessens on-chip SSN.

#### **2.4 Logic Circuits**

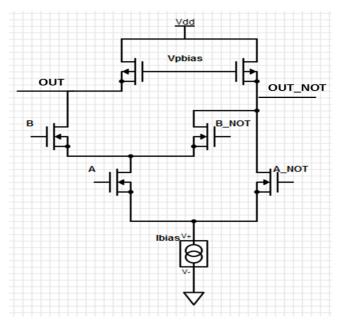

Basic MCML gates share certain standard characteristics. Only one gate, therefore, needs to be optimized. NAND, AND, NOR and OR gates are considered in this work. These gates are based on the circuit shown in Figure 1.

Figure 1. MCML Universal Gate[5]

#### 3. SIMULATIONS AND RESULTS

The simulations are based on 16 nm low power technology models.

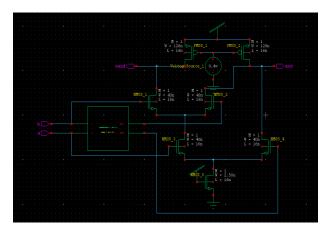

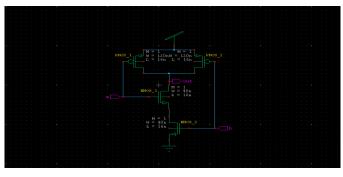

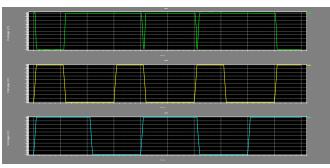

Here are the figures showing the simulation results of universal gates by both CMOS as WELL as MCML Technology.

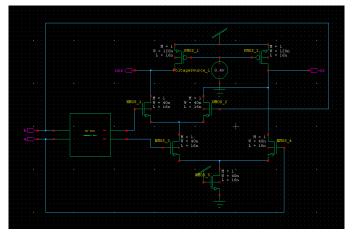

Figure 2. Schematic of AND/NAND using MCML

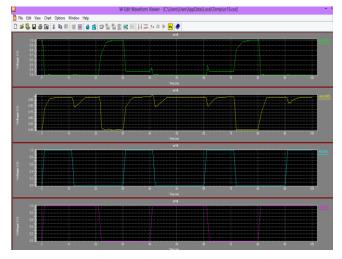

Figure 3. Waveform of AND/NAND using MCML

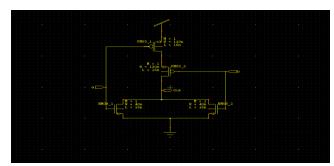

Figure 4. Schematic of NAND using CMOS

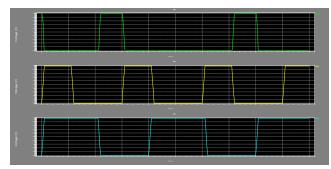

Figure 5. Waveform of NAND using CMOS

Figure 6. Schematic of OR/NOR using MCML

Figure 7. Waveform of OR/NOR using MCML

Figure 8. Schematic of NOR using CMOS

Figure 9. Waveform of NOR using CMOS

TABLE I. Power and Delay Analysis

| 1.347954e-004 | -2.0582e-008                   |

|---------------|--------------------------------|

| 6.502383e-008 | -9.9204e-009                   |

| 1.343237e-004 | 1.3086e-010                    |

| 4.135800e-008 | -1.2330e-010                   |

|               | 6.502383e-008<br>1.343237e-004 |

#### 4. CONCLUSION

From the above results we conclude that unlike standard CMOS, MCML Circuits perform better in terms of power and delay and therefore used in high speed circuits. From the Table 1 it can be concluded that circuits based on MCML

technology consumes less power and provides less delay as compared to conventional CMOS circuits. This paper has studied two-input universal gates implemented in the current mode technology (16nm) and concluded that MCML are faster than CMOS. Hence MCML topology shows more robustness against conventional CMOS.

#### 5. REFERENCES

- K. M. Sharaf and M.I. Elmasry, "An accmte analytical propagation delay model for high-speed CML bipolar circuits" IEEE JSSC, vol. 29, pp.31-45, Jan 1994.

- [2] K M. Sharaf and M.I. Elmasry, \*' Analysis and optimhtion of series gated CML and ECL bipolar circuits," IEEE JSSC, vol. 31,NO 2, pp.202-211, Feb. 1996.

- [3] P.K.Tien, "propagation delay in high speed Silicon bipolar and GaAs HBT digital circuits," ht. I. High speed electron, vol. 1, pp. 101-124,1990.

- [4] P. Gray, P. Hurst, S. Lewis and R. Meyer, Analysis and Design of Analog Integrated Circuits, John Wiley & Sons, 4th Edition, New York, 2000.

- [5] "Performance Characteristics of 14 nm Near Threshold MCML Circuits" presented at the IEEE S3S Conference 2013.

- [6] Hassan Hassan, Mohab Anis and Mohamed Elmasry "MOS Current Mode Logic: Design, Optimization, and Variability in IEEE 2004.

- [7] S.H. Amer, A.S. Emara, R. Mohie El-Din, M.M. Fouad, A.H. Madian, H.H. Amer, M.B. Abdelhalim and H.H. Draz "Testing Current Mode Two- Input Logic Gates", IEEE CCECE 2014 Toronto, Canada.

- [8] S. Khabiri and M. Shams, "Implementation of MCML universal logic gate for 10GHz-range in 0.13µm CMOS technology", Proceedings of the 2004 International Symposium on Circuits and Systems, Vancouver, Canada, vol. II, pp. 653-6, May 2004.