# **Bitonic Sorting Algorithm: A Review**

Megha Jain S.O.S In CS & IT, PT. Ravi Shankar Shukla University, Raipur (C.G), India Sanjay Kumar S.O.S In CS & IT, PT. Ravi Shankar Shukla University, Raipur (C.G), India V.K Patle S.O.S In CS & IT, PT. Ravi Shankar Shukla University, Raipur (C.G), India

### **ABSTRACT**

The Batcher's bitonic sorting algorithm is a parallel sorting algorithm, which is used for sorting the numbers in modern parallel machines. There are various parallel sorting algorithms such as radix sort, bitonic sort, etc. It is one of the efficient parallel sorting algorithm because of load balancing property. It is widely used in various scientific and engineering applications. However, Various researches have worked on a bitonic sorting algorithm in order to improve up the performance of original batcher's bitonic sorting algorithm. In this paper, tried to review the contribution made by these researchers.

# **Keywords**

Parallel Sort Algorithm, Bitonic Sort, Sorting Network.

#### 1. INTRODUCTION

Sorting in parallel machine is an interesting research area in both theoretical and practical significance. Sequential as well as parallel sorting are the most common activities in computing system. Sorting are integrated in computing system for efficient access of data when required. Introduction of bitonic sorting network in 1968 was adopted with one-to-one function i.e. route messages from one start node to one end node [1]. The Bitonic sorting algorithm discovered with oddeven network by Batcher. This algorithm is capable of sorting N keys in time complexity of O (log<sup>2</sup>N) with O (Nlog<sup>2</sup>N) comparators.

#### 1.1 Parallel Sort Algorithm

Parallel Sorting Algorithm is used in parallel computers for sorting the numbers. Sorting in parallel machine are achieved by dividing and computing data separately among processor. It generally requires a fixed number of mergers and exchange data operation. In parallel computer computation time decreases with the increase in the number of processors. There are several parallel sorting algorithms such as bitonic sort, radix sort [20] etc. Bitonic sort algorithm is efficient sorting algorithm among other parallel sorting algorithms. A load balancing feature of bitonic sort algorithm makes it unique. With load balancing feature, each processor under parallel machine maintain equal number of keys.

### 2. BITONIC SORT

Bitonic sort is a comparison-based sorting algorithm that can be run in parallel. It focuses on converting a random sequence of numbers into a *bitonic sequence*, one that monotonically increases, then decreases. More specifically, bitonic sort can be modelled as a type of *sorting network*. The algorithm, created by Ken Batcher, in 1968, consists of two parts. First, the unsorted sequence is built into a bitonic sequence; then, the series is split multiple times into smaller sequences until the input is in sorted order.

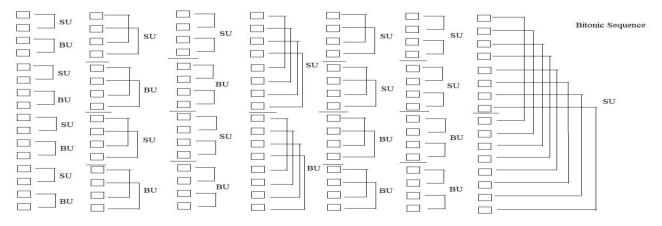

# 2.1 Bitonic Sequence

A bitonic sequence of n elements ranges from  $x_0, \ldots, x_{n-1}$  with characteristics (a) Existence of the index i, where  $0 \le i \le n-1$ , such that there exist monotonically increasing sequence from  $x_0$  to  $x_i$ , and monotonically decreasing sequence from  $x_i$  to  $x_{n-1}$ .(b) Existence of the cyclic shift of indices by which characterics satisfy [10]. After applying the above characteristics bitonic sequence occur. The bitonic split operation is applied for producing two bitonic sequences on which merge and sort operation is applied as shown in Fig 1.

#### 3. SORTING NETWORK

Sorting networks, also known as comparison networks for sorting inputs. The comparison network consists components like wires and comparators. The initial unsorted sequence enters through input wires, where a series of comparators switch two entries to be in either increasing or decreasing order. The two input wire named as In (x) and In (y) performs min (x, y) i.e. SU stands for small upper or max (x, y) i.e. BU stands for big upper, functions which generate two output wire named as Out (x) and Out (y) [22] as shown in below Comparator fig 2a: Increment Comparator and 2b: Decrement Comparator.

Fig 2a: Increment Comparator

Fig 2b: Decrement Comparator

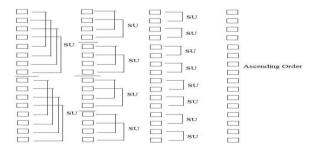

# 3.1 Bitonic Sorting Network

The Bitonic sorting network is one of the ways of constructing merging networks from comparison elements. It has the advantage of flexibility i.e. one network can accommodate input lists of various lengths and of modularity i.e. a large network can be split up into several identical modules. It sort input by implementing bitonic merge. A Bitonic sorting network of N numbers consists of log N bitonic sorting stages, where  $i^{th}$  stage composed of  $\,N/2^i$  alternating increasing and decreasing bitonic merges of size  $2^i\,[10]$  as depicted in Fig 3.

Fig 3: Sorting network for 16 elements

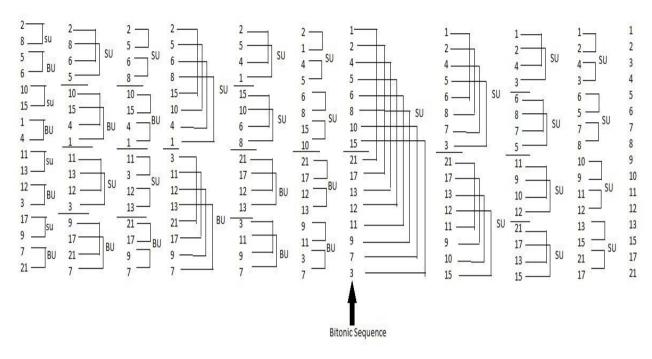

# 4. NUMERICAL EXAMPLE OF BITONIC SORT ALGORITHM

Here, we have randomly picked a data set of 16 elements, in order to sort elements using batcher's bitonic sort algorithm. 16 input elements are: 2, 8, 5, 6, 10, 15, 1, 4, 11, 13, 12, 3, 17, 9, 7, 21. Solution of bitonic sort algorithm depicted in Fig 4.

In Fig 4, Bitonic sequence generated by applying both Increment and Decrement comparator as stated above. Once we achieved sequence, which is monotonically increasing and monotonically decreasing known as bitonic sequence, thereafter we applied bitonic sorting network technique for achieving ascending order sorted elements. Thus 16 unsorted input elements after processing converted into 16 sorted output elements.

#### 5. LITERATURE REVIEW

A bitonic sorting algorithm with bit-level comparators, dynamic network and static network were introduced for handling one-to-many function.[1]. Fault detection algorithm is used to make comparisons among the links of bitonic sorting networks [2].Construct-BSNF algorithm gives rise of simple wiring interconnection through parity technique [3]. Parity strategy is used for simplifying the communication from O(Nlog<sup>2</sup>N) to O(NlogN) between communication links of the networks with the introduction of the recirculation bitonic sorting network [4]. Bitonic sorting is one of the parallel sorting algorithm, it efficiently sort N keys in O (log 2 N) time with O (N log2N) comparators [5].

VLSI implementation was proposed by M-algorithm implementation in which bitonic sorter acts as a base [6]. Modified version of bitonic sorting network named as Wafer Scale Integration uses self reconfigurable algorithm for dynamic fault tolerance [7]. Efficient Implementation of bitonic sorting on the amount of communication through Packed Exponential Connections [8]. For efficient performance of parallel machine new algorithm was also introduced known as A- Rank sort which was compared with bitonic sort algorithm [9]. Performance of bitonic sort algorithm, up to best can be achieved by increasing the number of processors. Remap-based algorithm is also one approach of optimization in parallel bitonic sort where data re maps of the smallest possible number are considered [10].

Batcher's bitonic sort can also be generalized in a k-way, called k-way bitonic sort [11].Batchers classic bitonic sorting network is as an example of hardware algorithms for sorting network of N elements with conflict-free memory accesses

[12]. Optimization in the communication process of merge and split steps is also one of the improved technique for bitonic sorting [13]. The Bitonic sort algorithm is also used for comparing the execution speed of the FPGA processing elements with the microprocessor processing elements [14].

Sorting of N2 elements in row-major order on a n\* n mesh connected computer in O (N) time [15]. However, with the combination of the bitonic merge sort algorithm with CCI (Compare and Conditionally Interchange) operations, an effort is made towards the improvement of parallel sorting algorithms for parallel machine [16]. Pleated cube-connected cycles (PCCC) implements optimal stable bitonic sorter in the synchronous VLSI model [17].

Bitonic sorter is the best approach for reconfigurable devices which provide enormous speedup [18]. Parallel and sequential bitonic, odd-even and rank-sort algorithms on different GPU and CPU analyzed with various performance metrics for better speed up [19]. However, a comparison between both bitonic sort and radix sort for sorting sequence on GPU and CPU environments for analyzing performance [20]. Interval Based Rearrangement [IBR] bitonic sorting algorithm is optimal when compared with an adaptive bitonic sorting algorithm for sorting sequences [21].

#### 6. CONCLUSION

Parallel computer consists of numbers of processor. Core are inbuilt in each processor for processing instruction. Such a computer is known as Multi-Core and Multiprocessor. The dual core processor is an example of parallel computer. Sorting in parallel computer is achieved by distribution of a data set among various processors. However, performance is not exactly double with the increase in numbers of cores, due to additional overheads of data transfers and barrier. Various researchers worked on bitonic sort algorithm for increasing performance. Researchers provide various approaches for reducing costs and increasing data access. Finally, reviewed the work done by researchers.

# 6.1 Future Work

At present performance as per survey is  $O\left(\log(n)^2\right)$ , in future work may be taken up to increase the performance by reducing complexity further.

### 7. ACKNOWLEDGMENTS

This work is supported by School of Studies in Computer Science & I.T, PT. Ravi Shankar Shukla University, Raipur, India.

Fig 1: Bitonic sequence of 16 elements

Fig 4: Steps of Batcher's Bitonic Sorting for 16 random elements.

### 8. REFERENCES

- [1] Majed 2. Al-Hajery and Kenneth E. Batcher "ON The Role Of K-Bits Bitonic Sorting Network In Multicast Routing\* ". Parallel and Distributed Processing, 1994. Proceedings. Sixth IEEE Symposium on 26-29 Oct 1994, on 706-714 page, 0-8186-6427-4/94.

- [2] Jae-Dong Lee and Kenneth E. Batcher. " A Bitonic Sorting Network with Simpler Flip Interconnections". Parallel Architectures, Algorithms, and Networks, 1996. Proceedings, Second International Symposium on 12-14 Jun 1996, page no. 104-109, 1087-4089.

- [3] Hongin Choi, Kenneth E. Batcher. "Fault Detection in Bitonic Sorting Networks". Parallel and Distributed Processing. 1995. Proceedings. seventh IEEE Symposium on 25-18 Oct 1995, page no. 266-270, 1063-6374.

- [4] Jae-dong Lee and Kenneth E. Batcher. "Minimizing Communication of a Recirculating Bitonic Sorting Network". Parallel Processing, 1996. Vol 3. Software, In the Proceeding 1 996 International Conference on Parallel Processing. At 12-16 Aug 1996, page no. 251-254 Vol 1, 0190-3918.

- [5] Jae-Dong Lee and Kenneth E. Batcher. "Minimizing Communication in the Bitonic Sort ". Parallel and Distributed Systems, IEEE Transactions on, Vol. 11, NO. 5, May 2000, page no. 459-474, 1045-9219.

- [6] Stanley J. Simmons." A Bitonic-Sorter based VLSI implementation of the M-Algorithm". IEEE Pacific Rim Conference on Communications, Computers and Signal Processing June 1st - 2nd, 1989, page no. 337-340.

- [7] Susumu Horiguchi Issei Numata Masayuki Kimura. " Self-Reconfigurable Algorithm of WSI Sorting Network ".In the Proceeding I991, Third International Conference on Wafer Scale Integration, on 29-31 Jan 1991, page no. 249-255.0-8186-9126-3.

- [8] Donna Quammen and Pearl Y. Wang "Bitonic Sorting on 2D-PEC: An Algorithmic Study on a Hierarchy of Meshes Network ". Parallel Processing Symposium, 1994. Proceedings., Eighth International, on 26-19 Apr 1994, page no. 418-423, 0-8186-5602-6.

- [9] Taoufik Dachraou, Lata Narayanan \*" Fast Deterministic Sorting on Large Parallel Machines ". Parallel and Distributed Processing, 1996., Eighth IEEE Symposium on 23-26 Oct 1996, page no. 273-280, 0-8186-7683-3.

- [10] Mihai Florin Ionescu and Klaus E. Schauser ." Optimizing Parallel Bitonic Sort ". Parallel Processing Symposium, 1997 . Proceedings., Eleventh International in 1-5 Apr, page no. 303-309, 1063-7133,0-8186-7793-7.

- [11] Toshio nakatani, Shing-tsaan huang, Bruce W. Arden, and Satish K. Tripath. "K-Way Bitonic Sort ". IEEE Transactions on computers, VOL. 38, NO. 2, FEBRUARY 1989, page no. 283-288, 0018-9340.

- [12] Stephan Olariu, Member, IEEE, M. Cristina Pinotti, Member, IEEE Computer Society, and Si Qing Zheng, Senior Member, IEEE. " An Optimal Hardware-Algorithm for Sorting Using a Fixed-Size Parallel Sorting Device ". IEEE Transactions on computers, VOL. 49, NO. 12, December 2000, page no. 1310-1324, 0018-9340.

- [13] Yong Cheol Kim, Minsoo Jeon, Dongseung Kim Andrew Sohn. "Communication-Efficient Bitonic Sort on a Distributed Memory Parallel Computer\* ". Parallel and Distributed Systems, 2001. ICPADS 2001. Proceedings. Eighth International Conference of 2001, page no. 165-170, 0-7695-1 153-8.

- [14] John Harkins, Tarek El-Ghazawi, Esam El-Araby, Miaoqing Huang. "Performance of Sorting Algorithms on the SRC 6 Reconfigurable Computer ". Field-Programmable Technology, 2005. Proceedings. 2005

- IEEE International Conference on 11-14 dec. 2005, page no. 295-296, 0-7803-9407-0.

- [15] David Nassimi and Sartaj sahini. "Bitonic Sort on a Mesh-Connected Parallel Computer ".IEEE transactions on computer, VOL. c-27, NO. 1, January 1979, page no. 2-7, 0018-9340.

- [16] Xie Hongwei Xue Yafeng. "An improved parallel sorting algorithm for odd sequence ". 2008 International Conference on Advanced Computer Theory and Engineering.ICACTE 08, on 20-22 Dec. 2008, page no. 356-360, 978-0-7695-3489-3.

- [17] Gianfranco bilardi, Student member, IEEE, and FRANCO P. PREPARATA, FELLOW, IEEE . " An Architecture for Bitonic Sorting with Optimal VLSI Performance". IEEE TRANSACTIONS ON COMPUTERS. VOL c-33, NO. 7, JUILY 1984, page no. 646-651.

- [18] J. Angermeier, E. Sibirko, R. Wanka, and J. Teich. " Bitonic Sorting on Dynamically Reconfigurable Architectures\* "Parallel & Distributed Processing Workshops and PhD Forum, 2011 IEEE International

- Symposium on 16-20 May 2011, page no. 314-317, 1530-2075.

- [19] Fiaz Gul Khan, Omar Usman Khan, Bartolomeo Montrucchio, Paolo Giaccone. "Analysis of Fast Parallel Sorting Algorithms for GPU Architectures' ". 2011 Frontiers of Information Technology, on 19-21 Dec, page no. 173-178,978-1-4673-0209-8.

- [20] Zehra YILDIZ, Musa AYDIN, Güray YILMAZ. " Paralleization of Bitonic sort and radix sort algorithms on many core GPUS ". Electronics, Computer and Computation(ICECCO), 2013 International Conference on 7-9 Nov. 2013, page no. 326-329, 978-1-4799-3343-3

- [21] Hagen Peters, Ole Schulz-Hildebrandt, Norbert Luttenberge." A novel sorting algorithm for many-core architectures based on adaptive bitonic sort ". 2012 IEEE 26th International Parallel and Distributed Processing Symposium, page no. 227-237.

- [22] https://mitpress.mit.edu/sites/default/files/Chapter%2027.pdf.

IJCA™: www.ijcaonline.org 43