# **Design of VCO for Microwave Frequency Band**

Ashish Mishra M.Tech (Dept. of E.C.E) G.L.A. University Mathura, India

## ABSTRACT

Voltage Controlled Oscillator (VCO) is an important building block in wireless communication system. In this paper a five stage current starved Voltage Controlled Oscillator (CMOS VCO) is designed which is used in Phase Lock Loop (PLL). The design is implemented on CADENCE VIRTUOSO Platform with high oscillation frequency and low power dissipation. The oscillation frequency of the designed VCO ranges from (665.7MHz-1.128GHz). The circuit is simulated using 180nm CMOS Technology. Simulation result shows that the power dissipation is -12dBm at power supply of 1.8 volt and the phase noise is (-105dBc/Hz @ 10MHz offset). The designing of such VCO shows the efficient performance of the oscillator circuit under given conditions. Such design is useful for frequency synthesizer application in PLL with less design cost.

#### **Keywords**

Cadence Virtuoso, Current Starved VCO, PLL, Frequency Synthesizer, Phase Noise

#### 1. INTRODUCTION

VCO is an essential block of the PLL in communication system. The design of such kind of VCO involves a trade-offs among power consumption, oscillation frequency, area occupied and speed of PLL. So it is important to estimate the oscillation frequency for the VCO. The main motivation behind the design of such type of several stages VCO is that how the power consumption and area occupied by the PLL circuit can be reduced up to the certain manner and also how can we evaluate the performance on the basis of high oscillation frequency and low phase noise as well as jitter [2],[4]. As the phase relationship between input reference data and feedback clock from VCO is not fixed and for reliable gain of high speed data, phase matching is essential for PLL [6].VCO is an essential block for several RF transceivers to select the frequency as well as to generate the signal. Recently RF transceivers acquire programmable carrier frequencies which depend upon PLL to accomplish that one. A less accurate oscillator circuit is required in the feedback path for a PLL which behaves as a control voltage function at the input. Mostly the oscillators in recent scenario require oscillators which are tunable. PLL is generally used for clock recovery, timing generation, FM & AM demodulation and as a frequency synthesizer in wireless communication system. Designing of CMOS-VCO can be done through many ways: by using LC-tank Circuit, Ring VCO, Relaxation Oscillator and Differential VCO circuits. In past years LC oscillator has depicted better phase noise performance because phase noise performance of such tuned VCO depends upon the Q- factor for LC-tank oscillator. Spiral inductor coils in LC-tank VCO requires some extra processing steps and designing cost, also there is a complications to control the eddy current. Tuning range is relatively low (10%-20%) for such VCO [1]-[5]. Also for high oscillation frequency the power consumption of ring Mr. Gaurav Kr. Sharma Astt. Prof. (Dept. of E.C.E) G.L.A. University Mathura, India

VCO may not be less for the equipments which are operates through battery [1], [17]. To overcome these problems, we are going to work on five stage current starved VCO and evaluate the performance parameters. This paper is divided into three sections: Section II: describes the schematic of VCO, Section III: shows the simulation results, finally the conclusion are taking place in Section IV.

#### 1.1 System Overview

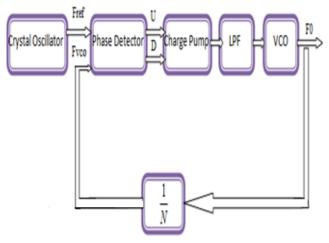

A PLL is a closed-loop feedback system which produces a fixed phase relationship between its output clock phase and reference clock signal at input side shown in figure 1. A PLL generally detects the phase change within the bandwidth of PLL. A PLL also generates multiple frequencies of higher range for a single reference input frequency. This phenomenon is called as frequency synthesis. Basically a PLL is a negative feedback control circuit. The main purpose of PLL is to match the phase of input reference signal with the feedback signal. If there is any mismatching occur in the phase after comparison then it perform several iterations until same phase is not found. This situation is called as lock mode. Still the iteration will be constant [13], [14].

- A PLL basically consists of five main blocks:

- 1. Phase Frequency Detector (PFD)

- 2. Charge Pump (CP)

- 3. Low Pass Filter (LPF)

- 4. Voltage Controlled Oscillator (VCO)

- 5. Divide by N Counter

Fig 1: Basic Block Diagram of PLL

# 2. CIRCUIT DESCRIPTION

# 2.1 Current Starved VCO

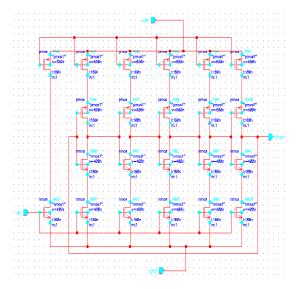

Figure 2 shows the schematic of five stage current starved VCO. The schematic shows that there are five inverter stages cascaded in the middle which produces anti high gain at the output of the VCO. There is two current starved circuits placed in the upper part (PMOS) and lower part (NMOS). The drain current is same between two MOSFETs placed in the leftmost which behaves as current sources. It means the inverter is current starved.

Fig 2: Designed Five Stage Current-Starved VCO

In such designed VCO basically five inverter stages are cascaded. Now the sizing of PMOS & NMOS transistors is done by the following equations given below.

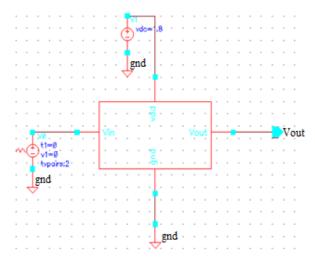

# 2.2 Test Circuit

In order to check the functionality of designed current-starved VCO, a test circuit is made using the symbol of VCO schematic cell. A ramp input is applied at input terminal of VCO and output is taken from  $V_{out}$  terminal. Figure 3 shows the test circuit of the VCO.

Fig 3: Test Circuit of VCO

# 2.3 Design Equations for VCO

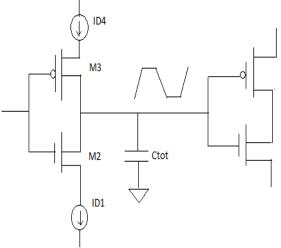

The sizing of each MOSFETs in the CMOS circuit can be done using the design equations, consider the simplified single stage inverter circuit of VCO shown in figure 4.

Fig 4: Single-Stage Inverter Circuit of VCO

Total Capacitance can be calculated as [5]:

$$C_{tot} = C_{out} + C_{in} = \frac{5}{2}C_{ox}(W_p L_p + W_n L_n)$$

(1)

Where gate-oxide capacitance is represented as  $C_{ox}$ ,

$$C_{OX} = \frac{\epsilon_r \ast \epsilon_0}{t_{ox}} \tag{2}$$

Charging time to charge  $C_{tot}$  for a constant current  $I_{D4}$  can be given as:

$$t_1 = C_{tot} * \frac{V_{SP}}{I_{D4}} \tag{3}$$

And discharging time to discharge  $C_{tot}$  for a constant current  $I_{D1}$  can be given as:

$$t_2 = C_{tot} * \frac{(V_{DD} - V_{SP})}{I_{D1}}$$

(4)

Total time when (  $\boldsymbol{I}_{D4}=\boldsymbol{I}_{D1}=\boldsymbol{I}_{D}$  ) can be given as:

$$(t_1 + t_2) = C_{tot} * \frac{V_{DD}}{I_D} = \frac{1}{T_d}$$

(5)

Frequency of oscillation can be given as [8]:

$$f_{osc} = \frac{1 * T_d}{N} = \frac{I_D}{N * C_{tot} * V_{DD}} = \frac{V_{DD}}{2} \quad (6)$$

Where  $T_d$  represent delay in time.  $f_{\it osc}$  will be equal to  $f_{\it center}$  if

$$V_{inVCO} = \frac{V_{DD}}{2}, I_D = I_{D cente}$$

N can be selected according to design. Drain current can be formed as:

$$I_{Dcenter} = N * C_{tot} * V_{DD} * f_{center}$$

(7)

The size of Current Starved Circuit can be calculated as [7]:  $\beta(V - V)^2$

$$I_{Dcenter} = \frac{\rho(v_{gs} - v_{thn})}{2} \tag{8}$$

Where

$$\beta = \frac{K_p * W}{L} = \frac{\mu * C_{ox} * W}{L}$$

# 3. SIMULATION RESULTS

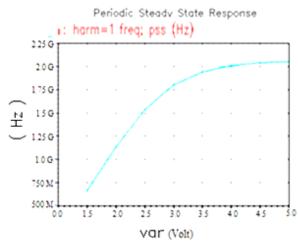

Fig 5: Oscillation Frequency Vs Control Voltage Plot

The plot in figure 5 shows the variation of oscillation frequency according to the control voltage at input. This shows the range of frequency upto which the plot is linear. The plot is linear in the range of (665.7MHz-1.128GHz).

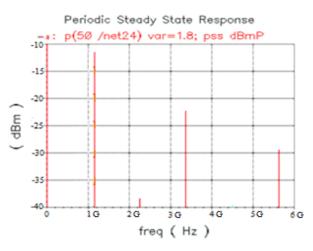

Fig 6: Output Power Vs Oscillation Frequency

The plot in figure 6 shows that the output power is -12dBm for Supply voltage of 1.8V.

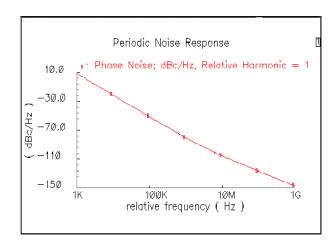

Fig 7: Phase noise Vs frequency

The plot in figure 7 shows that the phase noise is -105dBc/Hz @10 MHz offset.

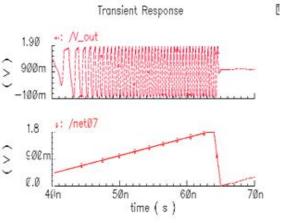

Fig 8: Output voltage Vs Time

The plot in figure 8 shows the transient response of the VCO which is in the form of oscillations.

#### Table 1. Comparison Table for Performance of Different VCOs at 0.18um Technology

|            |         | r           |          |             |

|------------|---------|-------------|----------|-------------|

| Topology   | Supply  | Centre      | Phase    | Power       |

|            | Voltage | Frequency/  | Noise    | Dissipation |

|            | (Volt)  | Oscillation | (dbc/Hz) |             |

|            |         | Frequency   |          |             |

|            |         | Range (GHz) |          |             |

| Ring VCO   | 2.0     | 4.3-6.1     | -88@     | 80mW        |

| [6]        |         |             | 1MHz     |             |

| Ring VCO   | 1.8     | 5.0         | -82@     | 135mW       |

| [9]        |         |             | 1MHz     |             |

| Current    | 1.8     | 3.1         | -102@    | 4.32mW      |

| Reused LC- |         |             | 1MHz     |             |

| VCO [11]   |         |             | offset   |             |

| Ring VCO   | 1.8     | 2.3-2.8     | -94.6@   | 10.1mW      |

| [15]       |         |             | 1MHz     |             |

| Ring VCO   | 1.8     | 3.125       | -91@     | 12.6mW      |

| [16]       |         |             | 1MHz     |             |

| This Work  | 1.8     | 665.7-1.128 | -105@    | -12dbm      |

|            |         |             | 10MHz    |             |

# 4. CONCLUSION

Designed VCO is operating in the frequency range of 665.7MHz-1.128GHz.The phase noise is (-105dBc/Hz at 10MHz) and power dissipation is (-12dBm) which is very low as compared to other VCOs. The designed VCO can be used for GSM application and suitable for designing synthesizer circuit using PLL. Such technique can also be applied to other low voltage analog circuits and RF circuits to improve their performance.

## 5. **REFERENCES**

- T. H. Lee and A. Hajimiri, Oscillator-Phase-Noise: A tutorial, IEEE J.Solid-State Circuits, vol.35, pp.326-336, March 2000.

- [2] W. Shing, T. Yan and H. Cam Luong, "A 900-MHz CMOS Low-Phase Noise Voltage Controlled Ring Oscillator, IEEE Transactions on Circuits and System II: Analog and Digital Signal Processing, vol.48, pp.216-221, Feb.2001.

- [3] B. Razavi, "Design of Analog CMOS Integrated Circuits," Tata McGraw Hill Edition, 2001.

- [4] A. Maxim et al., "A low-jitter 125-1250 MHz processindependent 0.18µm CMOS PLL based on a samplereset loop filter," in IEEE Int. Solid State Circuits Conf. Dig. Tech. Papers, pp.394-395, Feb. 2001.

- [5] R. J. Baker and D. E. Boyce, "CMOS Circuit Design, Layout, and Simulation," IEEE Press Series on Microelectronic Systems, 2002.

- [6] R. Tao and M. Berroth, "5 GHz voltage controlled ring oscillator using source capacitively coupled current amplifier," Silicon Monolithic-Integrated Circuits in RF Systems, pp. 45-48, April 2003.

- [7] Sung-Mo (Steve) Kang and Y. Leblebici, "CMOS Digital Integrated Circuits: Analysis and Design," Tata McGraw-Hill Edition, 2003.

- [8] D. P. Bautista & M. L. Arnada, "A low power and high speed VCO Ring Oscillator Circuit & Systems," ISCAS'04. Page(S); IV-752-755, 2004.

- [9] Y. A. Eken and J. P. Ukemura "A 5.9-GHz Voltage Controlled Ring Oscillator in 0.18-um CMOS," IEEE Journal of Solid-State Circuits, vol. 39, no. 1, Jan. 2004.

- [10] W. Xin, Y. Dunshan and S. Sheng, "A full swing and low power voltage-controlled ring oscillator," IEEE Conference on Electronic Devices and Solid-State Circuits, Pages: 141-143, Dec. 2005.

- [11] N. J. Oh and S. G. Lee, "Current reused LC VCOs," IEEE Microwave Wireless Compon. Lett., vol 15, no.11, pp.736-738, Nov. 2005.

- [12] H. Janardhan, M. F. Wagdy, "Design of a 1GHz Digital PLL using 0.18um CMOS Technology" in 2006 Third International Conference on Information Technology: New Generations (ITNG'06).

- [13] de Paula, L. Severino, S. Bampi, E. Fabris, and A. A. Susin, "A high swing low power CMOS differential voltage-controlled ring oscillator." In Electronics, Circuits and Systems, 2007. ICECS 2007. 14th IEEE International Conference on, pp. 498-501. IEEE, 2007.

- [14] Li, Tianwang, Bo Ye, and J. Jiang. "0.5 V 1.3 GHz voltage controlled ring oscillator." In ASIC, 2009. ASICON'09. IEEE 8th International Conference on, pp. 1181-1184. IEEE, 2009.

- [15] Gui, Xiaoyan, and Michael M. Green. "High-speed CMOS ring oscillators with low supply sensitivity." In Custom Integrated Circuits Conference (CICC), 2010 IEEE, pp. 1-4. IEEE, 2010.

- [16] S. Azqueta, Carlis, S. Celma and F. Aznar, "A 0.18 um CMOS ring VCO for Clock and data recovery applications." Microelectronics Reliability 51, no. 12 (2011): 2351-2356.

- [17] Lee, T. Hsueh, and P. A. Abshire. "Design methodology for a low-frequency current-starved voltage-controlled oscillator with a frequency divider." In Circuits and Systems (MWSCAS), 2012 IEEE 55th International Midwest Symposium on, pp. 646-649. IEEE, 2012.