# Design and Analysis of High Performance Novel 3T XOR Gate based 32-bit Adder at 28nm Technology

Sherpal Kaur

M. Tech Student

Department of Electronics

Yadavindra College of Engineering

Talwandi Sabo (Pb.) - 151302

India

Parminder Singh

Assistant Professor

Department of Electronics

Yadavindra College of Engineering

Talwandi Sabo (Pb.) - 151302

India

### **ABSTRACT**

In this paper, we designed and simulated a low power one bit, 8-bit and 32-bit full adder circuits namely Novel 10T, N14T, FA24T, CPL (complementary pass-transistor logic) and DPL (double pass-transistor logic). All the adders are tested by using one bit, 8-bit and 32-bit ripple carry adder architecture using Tanner EDA tool version 13.0. The one bit Novel 10T, N14T, XOR/XNOR function technique has been used for the generation of full adders. The proposed design successfully works with the buffering circuit in the full adder design. All full adder circuits are simulated with T-SPICE using 28nm Technology with 500 Mega Hertz frequency at 0.9 volt supply voltage. Due to lesser length requirement in the individual transistor, all the design of adders require lesser area as compared to existing design results in the tables. There is also improvement in terms of power, delay and power-delayproduct (PDP).

### **Keywords**

Full adder, Ripple carry adder, Average power, Delay, Power-delay-product (PDP), Leakage power, Noise margin.

### 1. INTRODUCTION

With the increasing demand of high speed portable devices and electronic systems much of the research efforts is directed towards increasing the speed of digital systems which has made present day technologies as a powerful work stations, personal computers and high definition multimedia capabilities. Most of the above mention devices are portable and strongly dependent upon the battery power. The other reason is to save energy in battery operated instruments same as electronic watches where average power is in microwatts. Average power is calculated by given pulse widths at input. As the frequency is increasing, power consumption is increasing and also the reliability of the devices is decreasing that is why power saving is becoming the important requirement for low power design and also important parameter of digital VLSI design [6].

### 2. DESIGN OF FIVE TYPES OF FULL ADDERS

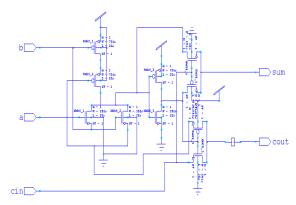

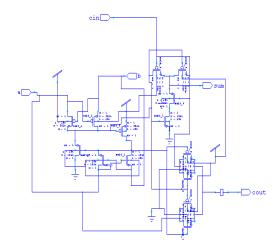

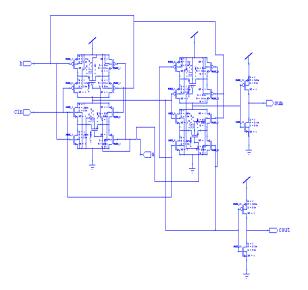

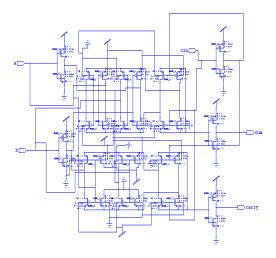

There are different types of CMOS full adder circuits. This section reviews the five styles of one bit full adder circuits, which are operated at 500 Mega Hertz frequency with 0.9 volt supply voltage by using 28nm Technology. The first full adder structure in this section one bit Novel 10T shown in Figure 1. N10T has 10 transistors. One bit N14T full adder with 14 transistors based on XOR gate and transmission gate multiplexer has been presented shown in Figure 2. One bit FA24T structure is shown in Figure 3. FA24T has 24 transistors. The structure of FA24T has two transistors less

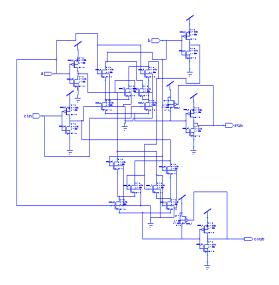

than bridge and has better power consumption. However, in FA24T the Sum generator should wait to receive the Cout signal from the Cout generator. Design of one bit complementary pass-transistor logic (CPL) type logic style, there are 24 transistors. Figure 4 shows circuit diagram of one bit CPL type adder Design of one bit double pass-transistor logic (DPL) is also designed, which has 34 transistors. Figure 5 shows circuit diagram of one bit DPL type adder.

Fig 1: Design of one bit N10T full adder

Fig 2: Design of one bit N14T full adder

Fig 3: Design of one bit FA24T full adder

Fig 4: Design of one bit CPL logic style full adder

Fig5:Design of one bit DPL logic style full adder

## 3. IMPLEMENTATION OF FULL ADDER CIRCUITS

One bit N10T and N14T full adder circuits are shown in Figure 1 and Figure 2. These circuits are XOR and XNOR gate based circuits. In the Novel 10T adder circuit, 3 transistors are used for generating of XOR functions [3]. In one-bit binary full adder, three one-bit inputs: A, B and Cin and outputs: sum and carry.

Sum =

$$(A \oplus B) \oplus Cin)$$

(1)

Carry = A. B + Cin  $(A \oplus B)$  (2)

The motive of this paper is to design a low power full adder circuit with the N10T method. The full adder circuit is shown in Figure 1. Compared to the various structures, a typical one bit full adder in N10T logic has only 10 transistors and the number of interconnections between them is highly reduced by using XOR/XNOR gates. In one bit complementary pass transistor (CPL) full adder, there are 24 transistors. In one bit double pass-transistor logic (DPL) full adder, there are 34 transistors.

### 4. SIMULATION RESULTS

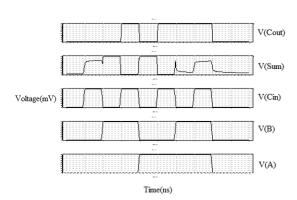

All full adder circuits operate in 500 Mega Hertz frequency range with voltage supply is 0.9 volt at 28nm technology by varying width. Output waveform of one bit N10T is shown in Figure 6, which shows better simulation results than other four types of full adders.

Fig 6: Output waveform of one bit N10T full adder

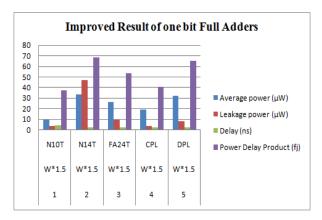

### 4.1 Simulation Result of One Bit Full Adders

In the Table 1, simulation results compared [3], [5] performance of full adders has been there, compared circuits [3] simulations are performed at 0.35µm Technology with 1.8 volt supply voltage, compared circuits [5] are performedat 0.18µm technology with 1.8 volt supply voltage and at 100MHz frequency, these results compared with present work. Simulation results compared[9], compared circuit [9] is performed at 0.18µm technology with 1.8 volt supply voltage in 200MHz frequency range, result [9] compared with present work. In compared results [3], [5], [9], leakage power is not measured. Table 1 shows simulation result of one bit full adders compared. In the present work, circuits operate in 500 Mega Hertz frequency with 0.9 volt supply voltage at 28nm Technology and leakage power is also measured in the present work.

|           |                                | [3]     |        | [5]     |        | [9]    | Present Work    |                 |                  |             |             |

|-----------|--------------------------------|---------|--------|---------|--------|--------|-----------------|-----------------|------------------|-------------|-------------|

| S.<br>No. | Parameters                     | N14T    | N10T   | FA24T   | CPL    | DPL    | N10T<br>(W*1.5) | N14T<br>(W*1.5) | FA24T<br>(W*1.5) | CPL (W*1.5) | DPL (W*1.5) |

| 1         | SupplyVolta<br>ge (V)          | 1.8     | 1.8    | 1.8     | 1.8    | 1.8    | 0.9             | 0.9             | 0.9              | 0.9         | 0.9         |

| 2         | Technology (nm)                | 350     | 180    | 180     | 180    | 180    | 28              | 28              | 28               | 28          | 28          |

| 3         | Average<br>Power (µW)          | 132.003 | 1.13   | 1.66    | 2.5    | 184.8  | 9.14            | 33.38           | 25.80            | 18.80       | 31.55       |

| 4         | Maximum<br>Delay (ns)          | 0.16    | 73.5   | 137.9   | 141.1  | 0.28   | 4.03            | 2.04            | 2.06             | 2.16        | 2.06        |

| 5         | Power<br>DelayProdu<br>ct (fj) | 21.120  | 83.055 | 228.914 | 352.75 | 51.744 | 36.834          | 68.095          | 53.148           | 40.608      | 64.993      |

| 6         | Leakage<br>Power (µW)          |         |        |         |        |        | 2.93            | 47.09           | 9.15             | 3.01        | 7.88        |

| 7         | No. of<br>Transistors          | 14      | 10     | 24      | 18     | 32     | 10              | 14              | 24               | 24          | 34          |

Table 1: Result of five types of one bit full adders compared

Graph of one bit N10T, N14T, FA24T, CPL and DPL type full adders

# **4.2 Simulation Result of 8-Bit Ripple Carry Adders**

In Table 2,N10T (CLRCL-Complementary and Level Restoring Carry Logic) [10] is performed at  $0.35\mu m$  Technology with 3.3 volt supply voltage in 132 Mega Hertz frequency. N14T [10] is performed at  $0.35\mu m$  Technology with 3.3volt supply voltage in 273 Mega Hertz frequency. In this result [10], leakage power is not measured. Present workperforms in 500 Mega Hertz frequency with 0.9 volt supply voltage at 28nm Technology.

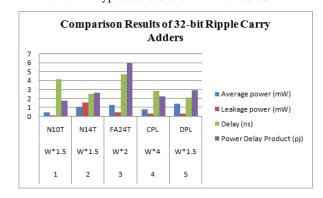

# **4.3 Simulation Result of 32-Bit Ripple Carry Adders**

Comparison result of 32-bit N10T, N14T, FA24T, CPL, DPL type ripple carry adders are given in the Table 3. In these types of adders, N10T is better than all other four types of adders, which has lesser average power and power-delay-product. CPL and DPL type full adders have also lesser power-delay-product as compared to FA24T full adder. CPL type adder has lesser average power as compared to N14T, FA24T and DPL type adders as shown in the Table 3.

Graph of 32- bit N10T, N14T, FA24T, CPL and DPL type ripple carry adders

Table 2: Result of five types of 8-bit ripple carry adders compared

|           |                                | [10]            |       | Present Work     |                  |                    |               |                 |  |

|-----------|--------------------------------|-----------------|-------|------------------|------------------|--------------------|---------------|-----------------|--|

| S.<br>No. | Parameters                     | N10T(CL<br>RCL) | N14T  | N10T(Width *1.5) | N14T(Width *1.5) | FA24T(Wi<br>dth*2) | CPL(Width *4) | DPL(Width* 2.5) |  |

| 1         | Supply<br>Voltage (V)          | 3.3             | 3.3   | 0.9              | 0.9              | 0.9                | 0.9           | 0.9             |  |

| 2         | Technology (nm)                | 350             | 350   | 28               | 28               | 28                 | 28            | 28              |  |

| 3         | Average<br>Power<br>(µW)       | 0.783           | 0.812 | 105.38           | 319.34           | 204.83             | 191.45        | 405.61          |  |

| 4         | Delay(ns)                      | 7.43            | 3.66  | 0.98             | 0.57             | 0.92               | 0.66          | 0.37            |  |

| 5         | Power<br>DelayProdu<br>ct (fj) | 5.817           | 2.971 | 103.272          | 182.023          | 188.443            | 126.357       | 150.075         |  |

| 6         | Leakage<br>Power (µW)          |                 |       | 24.65            | 377.96           | 98.19              | 66.31         | 106.75          |  |

Table 3: Result of five types of 32-bit ripple carry adders compared at 500MHz frequency by using 28nm technology

| S.  | Parameters                    | N10T(Width*1.5) | N14T(Width*1.5) | FA24T(Width*2) | CPL(Width*4) | DPL(Width*1.5) |

|-----|-------------------------------|-----------------|-----------------|----------------|--------------|----------------|

| No. |                               |                 |                 |                |              |                |

| 1   | Supply<br>Voltage (V)         | 0.9             | 0.9             | 0.9            | 0.9          | 0.9            |

| 2   | Average power (mW)            | 0.42            | 1.05            | 1.28           | 0.79         | 1.39           |

| 3   | Delay(ns)                     | 4.14            | 2.48            | 4.70           | 2.83         | 2.09           |

| 4   | Power<br>DelayProduct<br>(pj) | 1.738           | 2.604           | 6.016          | 2.235        | 2.905          |

| 5   | Leakage<br>power (mW)         | 0.09            | 1.51            | 0.39           | 0.26         | 0.25           |

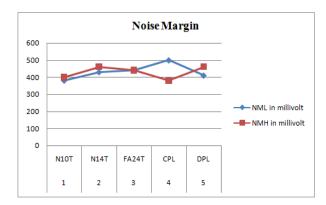

# **4.4** Noise Margin of XOR Gate Based One Bit Full Adders

Noise margin is calculated from the formula given below [2]:

$NM\mathsf{L} = V\mathsf{I}\mathsf{L}\text{-}V\mathsf{O}\mathsf{L}$

NMH = VOH-VIH

Noise margin is the amount by which a signal exceeds the minimum amount of proper operation. In VLSI system, Noise margin (in circuits) is the amount of noise that a circuit

couldwithstand without compromising the operation of the circuit. Noise margin at low voltage and noise margin at high voltage of one bit N10T, N14T, FA24T, CPL, DPL type full adders are shown in the Table 4. N10T has lesser noise margin at low voltage level as compared to other four types of full adders.

Table 4: Result of noise margin of five types of one bit full adders

| Name<br>of<br>Adder | VILin<br>volt | VOLi<br>nvol<br>t | VOH=<br>VDDin<br>volt | VIHin<br>volt | NMLi<br>nmV | NMH<br>in mV |

|---------------------|---------------|-------------------|-----------------------|---------------|-------------|--------------|

| N10T                | 0.380         | 0                 | 0.9                   | 0.500         | 380         | 400          |

| N14T                | 0.430         | 0                 | 0.9                   | 0.440         | 430         | 460          |

| FA24T               | 0.440         | 0                 | 0.9                   | 0.460         | 440         | 440          |

| CPL                 | 0.500         | 0                 | 0.9                   | 0.520         | 500         | 380          |

| DPL                 | 0.410         | 0                 | 0.9                   | 0.440         | 410         | 460          |

Graph of noise margin of one bit N10T, N14T, FA24T, CPL and DPL type full adders

### 5. CONCLUSION

In the present work, five types of one bit, 8-bit, 32-bit full adder circuits are designed based on ripple carry adder architecture with T-spice simulation from the netlists, in 500MHz frequency with 0.9v supply voltage at 28nm technology. The aim of this work had been power and delay reduction in the full adder circuit. In this operation, N10T, N14T, FA24T, CPL, DPL adders are introduced. Delay of one bit N10T is 94.51% improved and 55.65% power-delayproduct (PDP) improved [5]. In case of one bit N14T, average power is 74.71% improved [3] and one bit FA24T, delay is 98.50% improved and PDP 76.78% improved [5]. In case of one bit CPL, delay is 98.46% improved and PDP 88.48% improved [5] and one bit DPL, average power is 82.92% improved [9]. In case of 8-bit N10T, delay is 86.81% improved and delay of 8-bit N14T is 84.42% improved [10]. In case of 32-bit adder circuits, result of N10T adder circuit is better than four other types of adders. From present work, result of N10T is better than four other types of adders. All the designed adder circuits in this paper can be optimized for higher frequency range up to GHz. Reduction in area and improvement innoise margin can be the future scope of this paper.

### 6. ACKNOWLEDGEMENTS

Firstly, I thank the Lord Almighty who empowered me with the intellect and the belief to do this work. I also acknowledge with gratitude of my honourable guide Er. Parminder Singh (Assistant Professor), Department of Electronics and Communication Engineering Section, Yadavindra College of Engineering. A heartfelt thanks to my parents for the ever encouraging role. I would also like to thank all the staff members of Yadavindra College of Engineering, who encouraged and inspired me in achieving higher goals.

### 7. REFERENCES

- Neil H. E. Weste, David Harris and Ayan Banerjee, "CMOS VLSI Design, a Circuit and System Perspective", Third Edition, Pearson Education, Inc., (2005).

- [2] Sung-Mo (Steve) Kang and Yusuf Leblebici, "CMOS Digital Integrated Circuits Analysis & Design", Tata McGraw-Hill, (2005).

- [3] Manoj Kumar, Sandeep K. Arya, and Sujata Pandey, "A New Low Power Single Bit Full Adder Design with 14 Transistors using Novel 3 Transistors XOR Gate", International Journal of Modeling and Optimization, vol. 2, No. 4, pp. 544-548, (August 2012).

- [4] Mohammad Hossein Moaiyeri, Reza Faghih Mirzaee and Keivan Navi, "Two New Low-Power and High Performance Full Adders", Journals of Computers, vol. 4, No.2, pp. 119-126, (Feb. 2009).

- [5] Amin Bazzazi, Alireza Mahini and Jelveh Jelini, "Low Power Full Adder Using 8T Structure", Proceedings of the International Multiconference of Engineers and Computer Scientists 2012, vol. 2, IMECS 2012, Hong Kong, (March 14-16, 2012).

- [6] Yongtae Kim, Yong Zhang and Peng Li, "An energy efficient approximate adder with carry skip for error resilient neuromorphic VLSI system", IEEE International Conference, vol. 23, Issue 11, pp. 130-137, (Nov. 2013).

- [7] Deepa Sinha, Tripti Sharma, K. G. Sharma, Prof. B. P. Singh, "Design and Analysis of Low Power 1-bit Full Adder Cell", IEEE International Conference, vol. 2, pp. 303-305, (April 8-10, 2011).

- [8] http://ptm.asu.edu/modelcard/LP/28nm\_LP.pm.

- [9] Mariano Aguirre-Hernandez and Monico Lineras-Aranda, "CMOS Full Adder For Energy-Efficient Arithmetic Applications", IEEE Transaction on Very Large Scale Integration (VLSI) Systems, vol. 19, No. 4, pp. 718-721, (April 2011).

- [10] Jin-Fa Lin, Yin-Tsung Hwang, Ming-Hwa Sheu and Cheng-Che Ho, "A Novel High-Speed and Energy Efficient 10-Transistors Full Adder Design", IEEE Transaction on Circuits and Systems-I: Regular papers, vol. 54, No. 5, pp. 1050-1059, (May 2007).

- [11] Ilham Hassoune, Denis Flandre, lan O'Conner and Jean-Didier Legat, "ULPFA: A New Efficient Design of a Power-Aware Full Adder", IEEE Transaction on Circuits and Systems-I: Regular papers, vol. 57, No. 8, pp. 2066-2074, (August 2010).

IJCATM: www.ijcaonline.org