# Power Optimization of 8:1 MUX using Transmission Gate Logic (TGL) with Power Gating Technique

Abhishek Dixit Research Scholar ITM Universe Gwalior, India Saurabh Khandelwal ITM University Gwalior, India Shyam Akashe Dept. of ECED ITM University Gwalior, India

### ABSTRACT

This paper aims at reducing power and energy dissipation in Transmission Gate Logic (TGL) Multiplexer CMOS circuits comprise of reducing the power supply voltages, power supply current and delay with economical charge recovery logic. This paper designs an 8:1 Multiplexer with CMOS Transmission Gate Logic (TGL) using the Power Gating Technique, which reduces the leakage power and leakage current in active mode. Power Gating Technique uses Transmission Gate Logic (TGL) based an 8:1 multiplexer circuit which removes the degraded output. The PMOS and NMOS transistors are connected together for strong output level. Power gating technique achieves 36% reduction of leakage current and 43% reduction of leakage power in active mode, A the results of this paper are simulated on cadence virtuoso tool realized in 45nm technology with reduction of 4.021fW power, 7.381pA current and 0.7V supply voltage.

# **Keywords**

Power Gating Technique, Transistor Gate Logic (TGL), Low Power, Leakage Circuit

### 1. INTRODUCTION

The paper makes an effort to increase prominence of transportable systems and wishes to limit power consumption which has light-emitting diode for speedy and innovative developments in low power VLSI design during the recent years. The developments include transportable device applications requiring low power consumption and high output because of their little chip size with large density of elements, redoubled complexity and high frequencies. An 8:1 Multiplexer may be the basic building block of the "switch logic". The Multiplexer circuit often wants to combine eight or a lot of digital signals onto one line, by inserting them there at totally different times. Technically, this can be referred to as time-division multiplexing. Multiplexers may also be used as programmable logic devices [1]. By specifying the logic arrangement within the input signals, a custom logic circuit is often created.

The selector inputs then act as the logic inputs. This can be particularly helpful in things which price may be an issue and for modularity. So study on Multiplexer is inevitable [2] [3]. At the circuit design level, the key potential for power stake exists by suggesting the correct selection of a logic design for implementing combinative circuits. Exploration of low power logic designs within the analysis however has mainly focused on specific logic cell, namely Multiplexers, utilized in arithmetic circuits. At higher frequency the CMOS logic will operate continuously with low power consumption [4] [5]. The various methods are widely used for reducing power dissipation in circuits, reducing switching activities, supply voltages and load capacitances [6] [7]. Many leakage reduction techniques have area unit which cut back leakage power within the circuit to a significant level. Power Gating has become one amongst the foremost widely used circuit design techniques for reducing leakage current in power dissipation [8] [9]. This paper concentrates on reduction of leakage power that happens throughout the transition from the sleep mode to the active mode. This paper designs low power 8:1 Multiplexer using various CMOS designs like pass semiconductor device, transmission gate and Power Gating Technique. The Multiplexer has been realized with stacking power gating leakage reduction technique in 45 nanometer technology [10] [11].

# 2. 8:1 MULTIPLEXER

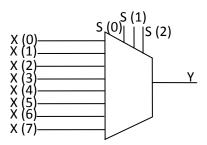

An 8:1 Multiplexer sends one of  $2^n$  input lines to a single output line. A Multiplexer has eight sets of input X (0), X (1), X (2), X (3), X (4), X (5), X (6), X (7) and three select lines S (0), S (1) and S (2). The Multiplexer output in a single bit Y, which is one of the  $2^n$  input data.

$$Y = X(0).\overline{S(0)}.\overline{S(1)}.\overline{S(2)} + X(1).S(0).\overline{S(1)}.\overline{S(2)} + X(2).\overline{S(0)}.S(1).\overline{S(2)} + X(3).S(0).S(1).\overline{S(2)} + X(4).\overline{S(0)}.\overline{S(1)}.S(2) + X(5).S(0).\overline{S(1)}.S(2) + X(6).\overline{S(2)}.S(1).S(0) + X(7).S(0).S(1).S(2)$$

(1)

Fig 1: Conventional 8:1 MUX

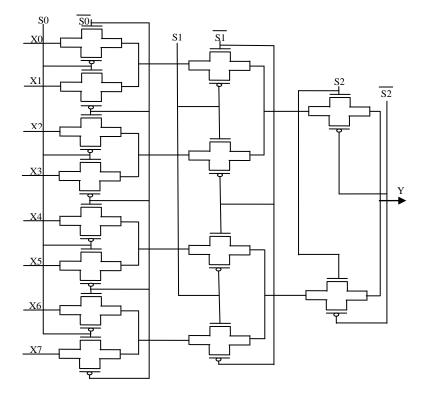

# 2.1Transmission Gate Logic (TGL) Based 8:1 Multiplexer

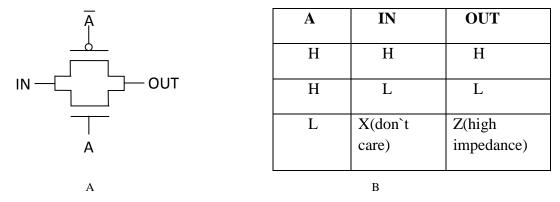

The CMOS Transmission Gate uses Transmission Gate Logic to appreciate advanced logic functions employing a little range of complementary transistors. It solves the matter of low logic level using PMOS as well as NMOS [11].

Transmission gate has a switch with low resistance and capacitance having ratio less logic. Also, DC characteristic of this gate is independent of input levels. It is designed by connecting each source to source and drain to drain terminal of NMOS and PMOS transistors. Because the NMOS transistor is passing strong signal '0' and PMOS transistors passes strong signal '1' towards the output,

$Fig\ 2\hbox{:}\ (A)\ Transmission\ Gate\ (B)\ Truth\ Table$

Fig 3: TGL base 8:1 MUX

each transistor is flipped on-off by the enable signals. The voltage on A node is a Logic one, the complementary Logic zero is applied to active-low A node. It permits each transistor to conduct and pass the signal from IN to OUT. Once the voltage on active-low node A is a Logic zero, the complementary Logic one is applied to node A turning each transistor OFF and forcing a high impedance condition on each IN and OUT node. The schematic diagram (Fig. 2) includes the absolute labels for IN and OUT, because the circuit will operate in a homogenous manner if that label were reversed. This design are provides true bidirectional property while not degrading input signal. The transmission gate symbol and the truth table are depicted in Fig. 2. [12] [13] [14].

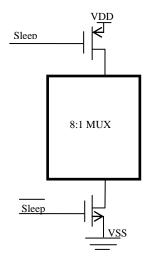

# 2.2 8:1 Multiplexer with Power Gating Technique

The Power Gating Technique reduces the leakage in every circuit, by inserting the NMOS and PMOS to the circuitry [15]. Fig. 4 shows the Power Gating circuit. Power Gating Technique is the most popular one for reducing the leakage in the circuits. Because of the simplicity of implementation of the technique, Power Gating has been used to minimize leakage energy in circuits at the architectural level [16] [17]. The effectiveness of Power Gating requires the following;

- The switches for turning OFF and ON of the functional unit at circuit level.

- These switches controls the power gate at various parts

of the circuit which act as handles at the system level

thereby giving the system software or the compiler the

ability to control them.

A sleep control mechanism is used for efficient power management. In the active mode, sleep is set to 'low' and sleep controlled transistor is turned ON. Since their resistance is small, the supply voltage VDD and VSS (GND) functions as real power line. In standby mode, sleep is set to 'high' and transistors are turned OFF, and leakage current is 'low'. In fact only one type of transistor is enough for the leakage control. Power Gating is a technique that can be easily implemented on 8:1 MUX circuits. Power Gating can reduce the leakage power, leakage current and delay. For PMOS and NMOS insertion, applied voltage on gate is 0v in active mode and virtual VDD line is connected to the supply VDD [18].

#### 3. SIMULATION RESULT

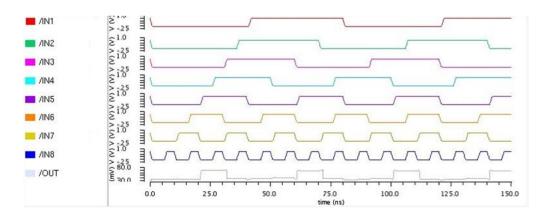

In this section the result of Transmission Gate Logic (TGL) and Power Gating TGL type Multiplexer has been calculated. Fig.5 shows the Transient Response of 8:1 Multiplexer.

Fig 4: Power Gating 8:1 MUX

Fig 5: Input and Output of 8:1 MUX

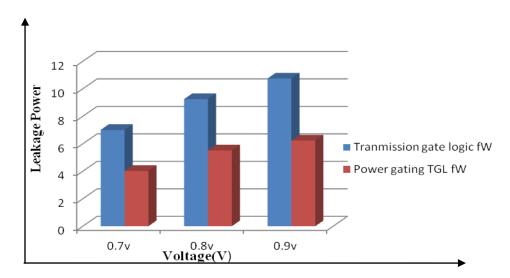

# 3.1 Leakage Power

The leakage power of the circuit is measured during the standby mode. It explains how large percentage of power is wasted by the whole circuit during OFF state when there is no supply. The leakage power is product of leakage current and supply voltage [19]. The basic equation of leakage power is displayed in Eq. (2).

#### $Pleak = I leak \times VDD (2)$

Where leak = leakage current, VDD = supply voltage.

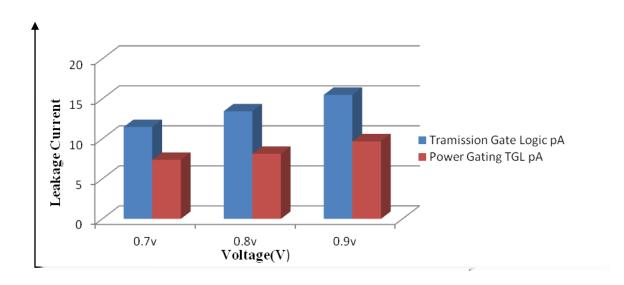

# 3.2 Leakage Current

Leakage current of the MUX is estimated during the standby mode. To estimate the leakage current of the MUX, NMOS transistor is required to measure the leakage current that is connected at the pull down network below the whole circuit. The Sleep transistor is OFF for this technique whenever leakage current calculation is analyzed. Leakage current is derived and calculated through the equation given below [20].

$$I_{leak} = I_{sub-thr} + I_{gat-ox}$$

(3)

Where I sub-thr = sub-threshold leakage current, Igat-ox = gate-oxide leakage current

Fig 6: Leakage Power Comparison at Various Voltage Supplies

Fig 7: Leakage Current Comparison at Various Voltage supplies

$$I_{sub-threshold} = K_A W e^{\frac{-Vth}{nV\theta}} (1 - e^{\frac{-V}{V\theta}})$$

(4)

Where  $K_A$  and n are experimentally derived, W= gate width, Vth = threshold voltage, n = slope shape factor,  $V\Theta$  = thermal voltage

$$I_{\text{gat-ox}} = K_B W \left(\frac{V}{Tox}\right)^2 e^{\frac{\alpha Tox}{V}}$$

(5)

Where KB and  $\alpha$  are experimentally derived, Tox = oxide thickness

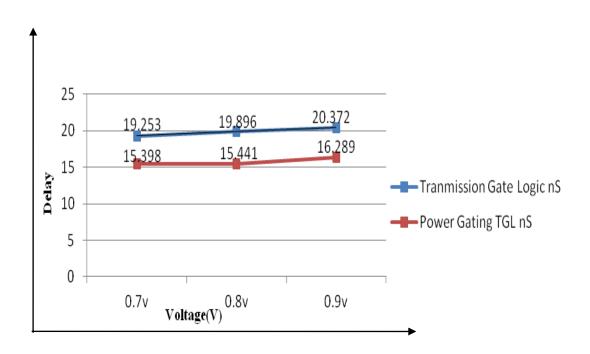

The design of logic signal delay is found to be necessary in every circuit. For this design, we need to find out the values of resistor that can introduce the delay on the signal lines. Delay of the circuit has depended on the value of the resistor itself as well as the capacitive load of the circuit [21]. The propagation delay of the RC circuit can be calculated by the Elmore model delay formula as follows:-

$$tp = 0.69Req \times CL$$

(6)

# 4. COMPRESSION RESULTS

This section compares the result of Multiplexer Design.

| Suppl<br>y<br>Volta<br>ge | Transmission Gate<br>Logic (TGL) |                                    |                              | Power Gating TGL  |                                    |                              |

|---------------------------|----------------------------------|------------------------------------|------------------------------|-------------------|------------------------------------|------------------------------|

|                           | Dela<br>y<br>(nS)                | Leaka<br>ge<br>Curre<br>nt<br>(pA) | Leaka<br>ge<br>Power<br>(fW) | Dela<br>y<br>(nS) | Leaka<br>ge<br>Curre<br>nt<br>(pA) | Leaka<br>ge<br>Power<br>(fW) |

| 0.7                       | 19.2<br>53                       | 11.48                              | 7.01                         | 15.3<br>98        | 7.381                              | 4.021                        |

| 0.8                       | 19.8<br>96                       | 13.45                              | 9.25                         | 15.4<br>41        | 8.137                              | 5.518                        |

| 0.9                       | 20.3<br>72                       | 15.50                              | 10.75                        | 16.2<br>89        | 9.692                              | 6.239                        |

Fig 8: Delay Comparison at Various Voltage Supplies

#### 5. CONCLUSION

This paper designs an 8:1 Multiplexer with Transmission Gate Logic using Power Gating Technique for reduction of leakage power and leakage current. The Transmission Gate Logic (TGL) using 28 transistors in the circuit is given in fig. 3. Reduction of power and current of Power Gating Technique is less as compared to Transmission Gate Logic (TGL). The result calculates in active mode with voltage variation. The 8:1 Multiplexer was designed using 45nm technology on cadence virtuoso tool. Using this tool the results have been calculated. Leakage power of 8:1 MUX Transmission Gate Logic (TGL) is 7.01fW and Power Gating Technique is 4.021fW. The leakage current of Transmission Gate Logic (TGL) is 11.48pA and Power Gating Technique is 7.381pA only.

#### 6. ACKNOWLEDGMENTS

This work is supported by ITM Universe Gwalior, in collaboration, with Cadence Design System, Bangalore.

#### 7. REFERENCES

- [1] Ila Gupta, Neha Arora and B.P Singh, "New Design of High Performance 2:1 Multiplexer", International Journal of Engineering Research and Applications (IJERA), vol. 2, no. 2, pp. 1492-1496, Apr 2012.

- [2] A. Bellaouar and Mohamed I. Elmasry, "Low-Power Digital VLSI Design: Circuits and Systems", 2nd Edition, pp.1-530, 1995.

- [3] Kang, Sung-Mo, Leblebici and Yusuf, "CMOS Digital Integrated Circuits Analysis and Design", McGraw-Hill International Editions, Boston, 3nd Edition, pp. 1-655, 2003.

- [4] Meenakshi Mishra and Shyam Akashe, "High Performance Low Power 200 Gb/s 4:1 MUX with TGL in 45 nm Technology", Journal of Applied Nanoscience, Springer, vol. 4, no. 3, pp 271-277, Feb. 2013.

- [5] Paul Metzgen, "A High Performance 32-bit ALU for Programmable Logic", In Proceedings of the 2004 ACM/SIGDA 12th International Symposium on Field Programmable Gate Arrays, pp. 61–70, 2004

- [6] Sarita, Jyoti Hooda, "Design and Implementation of Low Power 4:1 Multiplexer using Adiabatic Logic", International Journal of Innovative Technology and Exploring Engineering (IJITEE), vol. 2, no. 6, pp. 224-228, May 2013.

- [7] M. Pedram, "Power minimization in IC design: principles and applications", ACM Transactions on Design Automation of Electronic Systems, vol. 1, no. 1, pp. 3-56, Jan 1996.

- [8] S. Anvesh and P. Ramana Reddy, "Optimized Design of an Alu Block Using Power Gating Technique", IOSR Journal of Electronics and Communication Engineering (IOSR-JECE), vol. 4, no. 2, pp. 24-30, Dec 2012.

- [9] Saurabh Khandelwal, Shyam Akashe and Sanjay Sharma, "Supply Voltage Minimization Techniques for SRAM Leakage Reduction", Journal of Computational and Theoretical Nanoscience, vol. 9, no. 8, pp. 1044-1048, Aug 2012.

- [10] Bhanupriya Bhargava, Pradeep Kumar Sharma and Shyam Akashe "Reduction of Leakage Power using Stacking Power Gating Technique in Different CMOS

- Design Style at 45Nanometer Regime", International Journal of Computer Applications, vol. 83, no. 1, pp. 19-26, Dec 2013.

- [11] Ing-Chao Lin Chin-Hong Lin and Kuan-Hui Li, "Leakage and Aging Optimization Using Transmission Gate-Based Technique", IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 32, no. 1, pp. 87-99, Jan. 2013.

- [12] Shiv Shankar Mishra, Adarsh Kumar Agrawal and R.K. Nagaria "A comparative performance analysis of various CMOS design techniques for XOR and XNOR circuits", International Journal on Emerging Technologies, no. 10, pp. 1-10, Feb 2010.

- [13] Amreen parveen, Subhasis Bose and Sachin Bandewar " A High Speed Transmission Gate Logic Base 1/N Frequency Divider Digital Parallel Counter Design", International Journal of Engineering and Management Research, vol. 4, no.3, pp. 132-134, June 2014.

- [14] B.Vijayapriya, Dr.S. Padma and Prof.B.M.Prabhu, " Design of Low Power Novel Viterbi Decoder Using Transmission Gates", Int. Journal of Engineering Research and Applications, vol. 3, no. 6, pp. 972-976, Nov-Dec 2013.

- [15] N. Seki, L. Zhao, J. Kei, D. Ikebuchi, Y. Kojima, Y. Hasegawa, H. Amano, T. Kashima, S.Takeda, T. Shirai, M. Nakata, K. Usami, T. Sunata, J. Kanai, M. Namiki, M. Kondo, and H.Nakamura, "A fine grain dynamic sleep control scheme in MIPS R3000", In Proc. ICCD, pp. 612–617, Oct 2008.

- [16] D. Ikebuchi, N. Seki, Y. Kojima, M. Kamata, L. Zhao, H. Amano, T. Shirai, S. Koyama, T. Hashida, Y. Umahashi, H. Masuda, K. Usami, S.Takeda, H. Nakamura, M. Namiki, and M. Kondo, "Geyser-1: A MIPSR3000 CPU core with fine grain runtime power gating", In Proc. IEEE A-SSCC, pp. 281–284, Nov 2009.

- [17] K. Usami and N. Ohkubo, "A design approach for fine-grained run-time power gating using locally extracted sleep signals", In Proc. ICCD, pp. 155–161, Oct 2007.

- [18] Swati Mishra and Shyam Akashe, "Diode Based Ground Bounce Noise Reduction for 3-Bit Flash Analog to Digital Converter", International Journal of Advanced Science and Technology, vol. 57, pp. 63-74, August, 2013.

- [19] K. Roy, S. Mukhopadhyay and H. Mahmoodi-Meimand, "Leakage Current Mechanisms and Leakage Reduction Techniques in Deep-Submicron CMOS Circuits", In Proceedings of the IEEE, vol. 91, no. 2, pp. 305-327, Feb 2003

- [20] H. Jiao and V. Kursun, "Ground-Bouncing-Noise-Aware Combinational MTCMOS Circuits", In Proceedings IEEE Transactions on Circuits and Systems, vol. 57, no. 8, pp. 2053-2065, Aug 2010.

- [21] Toshihide Suzuki, Member, IEEE, Yoichi Kawano, Yasuhiro Nakasha, Shinji Yamaura, Tsuyoshi Takahashi, Kozo Makiyama, and Tatsuya Hirose, "A 50-Gbit/s 450-mW Full-Rate 4:1 Multiplexer With Multiphase Clock Architecture in 0.13-µm InP HEMT Technology". IEEE Journal of Solid-State Circuits, vol. 42, no. 3, March 2007.

IJCA™: www.ijcaonline.org