# 30 BIT Hamming Code for Error Detection and Correction with Even Parity and Odd Parity Check Method by using VHDL

Brajesh Kumar Gupta M.Tech Scholar Electronics and Communication Department Jaipur National University, Jaipur (India)

#### ABSTRACT

Hamming code error detection and correction methodology is used for error free communication in communication system. In communication system information data transferred from source to destination by channel. In between source and destination data may be corrupted due to any type of noise. To find original information we use Hamming code error detection and correction technique.

In hamming code error detection and correction technique to get error free data at destination, we encrypt information data according to even and odd parity method before transmission of information at source end.

In hamming code with even and odd parity check method by using VHDL, we transmit 25 bit information data with 5 redundancy bits from source and receive this data at destination. To find the value of these redundancy bits we have two methods, one of them is even parity method and another is odd parity method. In this paper we have written VHDL code for both methods at source as well as destination side.

At the point of destination, we receive 30 bit data, which was transmitted by source end. This receives data may be corrupted due to noise. To remove this noise we find the address of error bit then correct them. For finding the location of error bit and correct them we have again two methods one of them is even parity check method and another is odd parity check method. To find the location of error bit and correct them we write code in VHDL for destination.

In this paper we have written VHDL code for finding error location and correct error bit. We have also written code for decrypt this 30 bit encrypted data into 25 bit information data. Because of this code there is no need to use another circuit for decryption of encrypted data.

Up to today, at destination we were using one circuit for correcting error bit and another circuit for finding the information data from encrypted data. Now we can use only one circuit for correction error bit and finding the actual information data.

In this paper , we have described how we can generate 5 redundancy bit for 25 bit information data to make 30 bit data string for transmission by even and odd parity check method at source end. How we can find accurate 25 bit information data at destination from even and odd parity check method. In this paper, we describe what is a Hamming code and how

In this paper, we describe what is a Hamming code and how its work in communication system at source and destination. Prof. Rajeshwar Lal Dua HOD, Electronics and Communication Department Jaipur National University, Jaipur (India)

How we can generate 30 bit code for transmission and how we can get 25 bit actual information data from 30 bit received corrupted (error free) data string at destination.

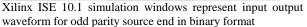

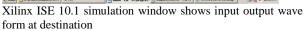

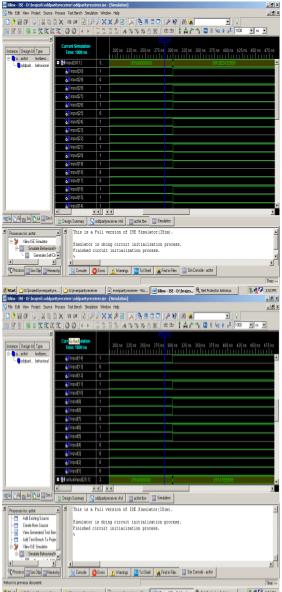

Here, we have used Xilinx ISE 10.1 Simulator for simulating VHDL Code. Xilinx ISE 10.1 Simulator is a simulator which is used for simulating HDL language and schematic circuit diagram. Here we have used Xilinx simulator to simulate VHDL code for transmitter and receiver.

**Keywords** – Hamming code, Odd parity check method, even parity check method, Redundancy bits, VHDL language, Xilinx ISE 10.1 Simulator.

# 1. INTRODUCTION

In communication system, a secure data transmission from transmitter to receiver is very major issue .for error free transmission there are number of technologies. One of them is hamming code method. Hamming code works on the parity check method. Parities are two types first even parity and second odd parity .here we use both even parity and odd parity method to encrypt data before transmission.

In this paper we generate 5 redundancy bits for 25 bit information data to send 30 bit data string for transmission at source by using even and odd parity check method[1][2][3].

Suppose, we want to transmit 25 information data bit is "1011111101110011001010110" = 25 h17EE656. For this 25 bit information data we need 5 redundancy bits and these are "00111" (5h'07) and "11000"(5h'18) by using even add odd parity method respectably. After generating redundancy bits, add these bits to 25 bit information data for making 30 bit data string for transmission at source end. How we can generate 5 redundancy bits for 25 bit information data for making 30 bit data string for transmission at source end by using even and odd parity method will be discussed in details at communication with even parity method and communication with odd parity method section[1][2][3].

At destination receiver receives 30 bit data string from channel and check it, is it corrupted or not? If this data string is corrupted then receiver find the error location according to parity check method (even parity check or odd parity check method which one we use for finding error). And correct this error bit.

In this paper receiver pass only 25 bit information after correcting error and decrypted 30 bit data.

How we can find error bit location, how receiver correct this error bit and how we get 25 bit actual information data from 30 bit encrypted data string will be discussed in details in communication with even parity method and communication with odd parity method section[1][2][3].

In this paper we have used VHDL language for writing VHDL code for source and destination. At source, VHDL code is used for generating 5 redundancy bits for 25 bit information data and also written code for making 30 bit data string for transmission. At destination, we have written VHDL code for finding error bit location and for correcting that error bit. At destination we have also written VHDL code for finding 25 bit actual information data from 30 bit received encrypted data[6][7][8][9][10].

Here we have used Xilinx ISE 10.1 simulator to simulate VHDL code and given simulated results in term of input output waveforms [4] [5].

# 2. HAMMING CODE

Hamming code is a linear error-correcting code named after its inventor, Richard Hamming. Hamming codes can detect up to two simultaneous bit errors, and correct single-bit errors; thus, reliable communication is possible when the Hamming distance between the transmitted and received bit patterns is less than or equal to one. By contrast, the simple parity code cannot correct errors, and can only detect an odd number of errors.

In 1950 Hamming introduced the (7, 4) code. It encodes 4 data bits into 7 bits by adding three parity bits. Hamming (7, 4) can detect and correct single – bit errors. With the addition of overall parity bit, it can also detect (but not correct) double bit errors. Hamming code is an improvement on parity check method. It can correct 1 error bit only[1][2][3].

Hamming code method works only two methods (even parity, odd parity) for generating redundancy bit. In hamming code method for generating the number of redundancy bit use formula .The number of redundancy depends on the number of information data bits[1][2][3].

Formula for generating redundancy bit ----

$2^{n} r >= D + r + 1$  ------(1)

Here r = number of redundancy bit

D = number of information data bit Calculate the number of number of redundancy bit for 25 bit of input data string by above formula We get 5 redundancy bit required.

# 2.1 Redundancy

To detect or correct the error we have to use some extra bits. These extra bits are called redundancy bits. We add these redundancy bits to the information data at the source end and remove at destination end. Presence of redundancy bit allows the receiver to detect or correct corrupted bits. The concept of including extra information in the transmission for error detection is a good one. But in place of repeating the entire data stream, a shorter group of bits may be added to the end of each unit. This technique is called redundancy because the extra bits are redundant to the information [7]

### 3. COMMUNICATION WITH EVEN PARITY CHECK METHOD

In communication system need two main part one them is source for sending data and another is destination for receives transmitted data. even parity check method count the number of one's if number of one's are even add zero (0) else add one (1). [1][2][3]

# **3.1 Source Section With Even Parity Method**

In this paper, here I want to transmit 25 bit information data string. To transmit 25 bit information data need minimum 5 redundancy bit according to equation (1). Suppose , these redundancy bits are r(1),r(2),r(3),r(4),r(5). To find the value Redundancy bit, H ere we use even parity check method. The value of redundancy bit can be finding by XORING of different location of information data bit for different redundancy bit. the property of XOR gate is that if number of one's are even in input its shows the output zero else its shows output one. By using this property we can easily find the number of one's in a given string are even or odd for a particular redundancy bit. [6][7][8][9][10]

Suppose, Here we apply information data bit is "1011111101110011001010110" = 25'h17EE656. Before transmission of information data bits we need to add 5 redundancy bits.

Calculation for redundancy bit r(1), By XORING input bit address given below

r(1) = 1,2,4,5,7,9,11,12,14,16,18,20,22,24.

Here the number of one's are 9, this is a even number so according to even parity method

The value of r(1) = 1

Calculation for redundancy bit r(2), r(4), r(8), r(16)

$\mathbf{r}(2) = 1,3,4,6,7,10,11,13,14,17,18,21,22,25$

r(4) = 2,3,4,8,9,10,11,15,16,17,18,23,24,25r(8) = 5,6,7,8,9,10,11,19,20,21,22,23,24,25

f(8) = 5,6,7,8,9,10,11,19,20,21,22,23,24,25

$\mathbf{r(16)} = 12,13,14,15,16,17,18,19,20,21,22,23,24,25$

For calculating the redundancy bit of r(2),r(4),r(8),r(16) count the number of one's for appropriate redundancy bit according to given formula above [1][2][3].

The value of r (2) is 1(the number of one's are 9) value of r (4) is 1(the number of one's are 9) the value of r (8) is 0 (the number of one's are 10) the value of r (16) is 0 (the number of one's are 10). [1][2][3][6][7]

The calculation of redundancy bit is done by VHDL code written in Xilinx ISE 10.1 project navigator window. And simulate this VHDL code by using Xilinx ISE 10.1 Simulator and get the value of redundancy bit. Now we know the value of redundancy bits are "00111" 5h'17. [5][6][8]

After calculation of redundancy bit, add these bits in information data and get encrypted 30 bit data string for transmission.

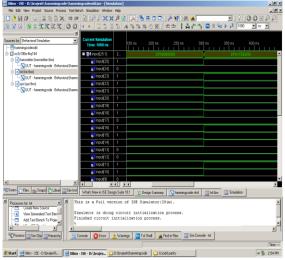

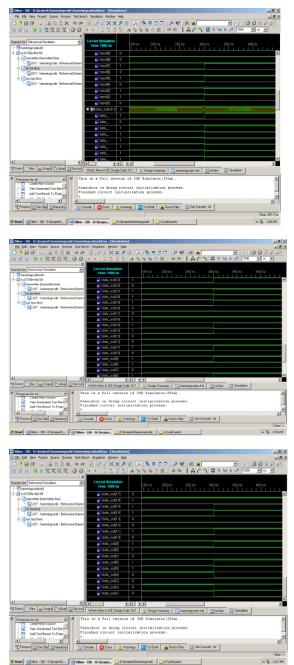

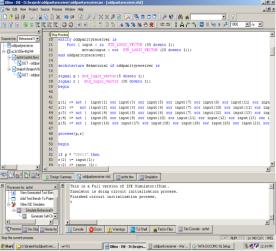

The encrypted30 bit data string is.... 101111110111000110010100111011 = 30`h2FDC653B. Input and output simulated results shown bellow in Xilinx ISE 10.1 simulation window. In Xilinx ISE 10.1 simulation window 25 bit information input data string and 30 bit encrypted data represented by input (25: 1) and data\_out(30:1) respectively.[5][6][10] VHDL code for source end shown in given below Xilinx ISE 10.1 project navigator window. [5][6]

| Pile Edit Vew Project Sour   | nningrode\hammingrode.ke - [hammingrode,vhd*]<br>ce Proces Window Help      | وا <u>د</u><br>نام        |

|------------------------------|-----------------------------------------------------------------------------|---------------------------|

|                              | 3 G X ∞ ∞ 0 10 0 X X 0 8 X X 0 8 0 0 10 10 10 0 0 0                         |                           |

| ि 🖌 🕑 🤇 🐲 🕉 🕄 🕄              | 第1年13日の14月前に1月1日日(14月1日)(14月1日)(14月1日)(14日))(14日)(14日)(14日)(14日)(14日)(14日)( |                           |

| X                            | 29                                                                          |                           |

| arces for Behavioral S 💌     | 30 entity hammingcode im                                                    |                           |

| hamningcode                  | 31 Port ( input : in STD_LOGIC_VECTOR (25 downto i))                        |                           |

| x:3:100e-4tq144              | 32 data_out : out STD_LOGIC_VECTOR (30 downto 1));                          |                           |

| E- Kanomitter (Isanom        | 33 end haswingcode;<br>34                                                   |                           |

| UUT - hamesir                | 35 architecture Behavioral of hammingcode is                                |                           |

| - a wz (wz.tbn)              | 36 signal r : std logic vector(30 downto 1);                                |                           |

| - OUUT - hanevir             | 17 signal p,q,s,t : std logic ;                                             |                           |

| <u> </u>                     | 38 begin                                                                    |                           |

|                              | 39 r(3) <= input(1);                                                        |                           |

|                              | 40 r(5) <= input(2);                                                        |                           |

|                              | 41 r(6) <= input(3);                                                        |                           |

|                              | 42 r(7) <= input(9);                                                        |                           |

|                              | 43 r(9) <= input(5);                                                        |                           |

|                              | <pre>44 r(10) &lt;= input(6);</pre>                                         |                           |

|                              | 45 r(11) <= input(7);                                                       |                           |

|                              | 46 r(12) <= input(0);<br>47 r(13) <= input(9);                              |                           |

|                              | 47 r(13) <= input(9);<br>48 r(14) <= input(10);                             |                           |

|                              | 49 r(15) <= input(11);                                                      |                           |

|                              | 50 r(17) <= input(12);                                                      |                           |

|                              | 51 r(18) <= input(13) j                                                     |                           |

|                              | 52 r(19) <= input(14);                                                      |                           |

|                              | 53 r(20) <= input(15))                                                      |                           |

|                              | 54 r(21) <= input(16):                                                      |                           |

|                              |                                                                             |                           |

| 50 📉 Fil 📷 Sne 🌔 Lit         | C Design Summary 💽 hammingcode vhd"                                         |                           |

| Processes for UUT - harmings | inde M                                                                      |                           |

| - Add Existing Source        | Started : "Launching Design Summary".                                       |                           |

| - Create New Source          | Started : "Launching ISE Text Editor to edit hammingcode, vhd",             |                           |

| 10 🎾 Xiinx ISE Simulator     | sources : sourcease and text Editor to edit numbingcode; vnd.,              |                           |

| -                            |                                                                             |                           |

|                              |                                                                             |                           |

| 4                            | A                                                                           |                           |

| Processes                    | 🚺 Console 👩 Exces 🔔 Warnings 🛄 Tel Shell 🙀 Find in Files                    |                           |

|                              |                                                                             | CAPS NUM SCR. In 29 Col 1 |

| Part Champonisticati         | m32 id Xilina - ISE - D\brajes                                              | P 📲 11:27                 |

VHDL code for even parity check method at source

Xilinx ISE 10.1 window shows Input output wave form in Hexadecimal format at source end

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | inx - 156 - D:\brajesh\hammingcode\)<br>e Edit Vew Project Source Process 1 | ammingcode.lae - [Simulation]<br>fextBench Simulation Window Help                                              | 1     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                             | 0 00 0 1 0 0 X X 0 0 X 3 8 8 0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0                                               |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | P P 8 2 70 90 90 90 10                                                      | O (+) I I I I A 74 74 76 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                 | •     |

| The leave is a set of the set of                        | - E                                                                         |                                                                                                                |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                             |                                                                                                                |       |

| Image: Second                                |                                                                             |                                                                                                                |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                             |                                                                                                                |       |

| Image:                                |                                                                             |                                                                                                                |       |

| Image: Section of the section of th                                |                                                                             |                                                                                                                |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                             |                                                                                                                |       |

| A weeks<br>A weeks                                                                                                                                                                                                                                                                                                                                    |                                                                             |                                                                                                                |       |

| A web 1 A web 2 A web 3 A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                             |                                                                                                                |       |

| A week 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                             |                                                                                                                |       |

| Interest in the second se      |                                                                             |                                                                                                                |       |

| A level 0 I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                             |                                                                                                                |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                             |                                                                                                                |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                             |                                                                                                                |       |

| Invite invi      |                                                                             |                                                                                                                |       |

| A web-1 A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                             |                                                                                                                |       |

| A Second Table and second table and a second table and a second table and a second t      |                                                                             |                                                                                                                |       |

| Compromentation C                                                                                                                                                                                                                                                                                                                                                                                                                              | input(10)                                                                   |                                                                                                                |       |

| Constraints and and a second and a second and a second and a second a       |                                                                             |                                                                                                                |       |

| Control of the second sec      |                                                                             |                                                                                                                |       |

| definition of the second       | Conditional and                                                             |                                                                                                                |       |

| the second rates of the second rate of the sec      | rocesses for transmitter                                                    | Fuse CPU Usage: 640 ns                                                                                         |       |

| A for the first of a former of the first of the      |                                                                             | This is a Full version of ISE Simulator (ISim) .                                                               |       |

| Image: Second                  | Cal Add Test Bench To Project                                               | Simulator is doing circuit initialization process.                                                             |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                             | Finished circuit initialization process.                                                                       |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Processe 🔄 Sin Obje 🔛 Hierarchy                                             | Conzole Conzole - transmitter                                                                                  |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                             |                                                                                                                | ne: 3 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | art Mine - Difestor                                                         |                                                                                                                |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | me 1St = D: braiesh barrening ode b                                         |                                                                                                                |       |

| Image: Second                         |                                                                             |                                                                                                                |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                             |                                                                                                                |       |

| All control     All control     Other                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                             |                                                                                                                | _     |

| The two w     P1 / 6     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 / 8     20 /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | REAL OF A STREET OF ST. 1 C                                                 |                                                                                                                | 1     |

| The two w     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P     P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Run Process and Inc.                                                        | and a second |       |

| A Nordy     0       A Nordy     1       A Nordy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                             |                                                                                                                |       |

| A and a function from the formed to the      |                                                                             |                                                                                                                |       |

| Subject     Image: Subject                                     | - hassnit                                                                   |                                                                                                                |       |

| Al andon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                             |                                                                                                                |       |

| Image: Second                         |                                                                             |                                                                                                                |       |

| Implicit     Implicit       Implici     Implici <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                             |                                                                                                                |       |

| All and before the result of the second for th      |                                                                             |                                                                                                                |       |

| Image: second                  |                                                                             |                                                                                                                |       |

| Image: Control of Con                        |                                                                             |                                                                                                                |       |

| A data comp     Image: Comp       Image: Comp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                             |                                                                                                                |       |

| A Tack untig 0 A Tack u                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                             |                                                                                                                |       |

| Construction C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                             |                                                                                                                |       |

| A f a control of a |                                                                             |                                                                                                                |       |

| Al La doct 1 A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                             |                                                                                                                |       |

| All and worthy Image: State of the state                               |                                                                             |                                                                                                                |       |

| All End-sufficient     Image: State                                      |                                                                             |                                                                                                                |       |

| Construction C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                             |                                                                                                                |       |

| Control C      | data_out[24]                                                                |                                                                                                                |       |

| Image: State Control     Transmitter       Image: State Control     Transmi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | data_out[23]                                                                | 1                                                                                                              |       |

| Construction C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3.1 @ata_out[22]                                                            | 0                                                                                                              |       |

| Control C      |                                                                             |                                                                                                                |       |