# A Simulation Algorithm for Prediction of Random Variations in Digital Circuits

Hamid Reza Shokuhfar M.Sc, Department of Electrical and Computer Engineering, University of Kashan, Iran. Daryoosh Dideban

Assistant Professor

1-Department of Electrical and

Comp. Engineering, University

of Kashan,, Iran.2-Institute of

Nanoscience and

Nanotechnology, University of

Kashan, Iran.

Negin Moezi

Assistant Professor

1-Institute of Nanoscience and

Nanotechnology, University of

Kashan, Iran, 2- Technical and

Vocational University,

Kashan, Iran.

Hamed Jooypa

M.Sc. student,

Department of Electrical and Computer Engineering,

University of Kashan,

Kashan, Iran.

### **ABSTRACT**

A novel simulation algorithm capable of capturing statistical variability manifests in digital design is proposed. The only estimations for the algorithm inputs are the standard deviations of channel length and the gate voltage. Implementing the algorithm for the simulation of propagation delay times of the basic digital building blocks such as inverter, NAND2 and NOR2 circuits gives errors less than 7% against the most accurate results obtained from 'atomistic' HSPICE simulations.

### **Keywords**

Statistical variability, Digital design, Monte-Carlo simulation, statistical modeling, nano-CMOS

### 1. INTRODUCTION

Aggressive scaling of device dimensions into ultra short channel regime leads to significant process and intrinsic parameter fluctuations [1-3]. These fluctuations have caused reliability issues which in turn results in a waste of both time and cost. It is therefore important that a circuit designer can incorporate these effects in early simulation stage. A variability-aware design approach needs a right prediction of random variations [4-7]. The investigation and analyze of these variations using accurate 'atomistic' simulations needs both long times and powerful computational resources [1]. On the other hand, the outcomes of 'atomistic' simulations are not widely accessible for the designers.

An extensive study has been carried out in the literature to incorporate the impact of random variations into analytical expressions in digital circuit design and thus, simplifying the complexity of 'atomistic' simulations. However, those expressions suffering from common issues: (i)-they are all circuit specific, (ii)-their accuracy depends to input slew rate and load capacitance[8-11]

This paper organizes as follows. Section 2 reviews some analytical expressions capable of dealing with variations in inverters as the most important digital building blocks. Section 3 proposes an algorithm to account for the random variations inthe gate propagation delay time using appropriate Gaussian sources in series with the device and embedding length variations in HSPICE circuit netlist. Section 4

implements the algorithm and extends its usage on NAND2 and NOR2 gates. Accurate Monte-Carlo statistical simulations have been carried out to compare the accuracy of the proposed algorithm against 'atomistic' results.

### 2. ANALYTICAL MODELING OF PROPAGATION DELAY TIME

Due to CMOS short channel effects arising from the device scaling into deca-nanometer dimensions, prediction of device current (Ids) using standard Shockley model results in significant errors. The Alpha power law model introduced by Sakurai and Newton is among the first ones incorporating carrier velocity saturation effects [8]. However, this model ignores the saturation current variations and thus, results in large deviations in Ids and the inverter propagation delay time (Tpd). Some other useful models have been introduced in the literatures which have their advantages and drawbacks [9,10]. For instance, some modifications in Alpha-power law have been proposed resulted in reduced errors in Ids but they ignore gate-drain capacitance or over-shoot and short circuit current [11].

Since any deviation in Ids causes significant error in the Tpd, the Alpha-power law will not be used for sub-50nm technologies. This is due to the fact that the channel length modulation effect is not considered effectively in this model. The selected model should take the device channel modulation effect into account. The current in this model is given by [12]:

$$I_{D} = \begin{cases} 0, & (V_{GS} \leq V_{th} : cutoff) \\ \beta_{t} (V_{in} - V_{th})^{\alpha} V_{DS}, & (V_{DS} < V_{DSAT} : linear) \\ \beta_{s} (V_{in} - V_{th})^{\alpha} \left[ 1 + \lambda (V_{DS} - V_{DD}) \right], & (V_{DS} \geq V_{DSAT} : saturation) \end{cases}$$

(1)

Where:

$$\beta_{l} = \frac{\beta_{s} \left[ 1 + \lambda \left( V_{DSAT} - V_{DD} \right) \right]}{V_{DSAT}}$$

$$\beta_s = \frac{I_{D0}}{\left(1 - \frac{V_{th}}{V_{DD}}\right)^{\alpha}}$$

Where  $V_{DSAT}$  is the drain saturation voltage at  $V_{GS} = V_{DD}$  and  $\alpha$  is the velocity saturation index. Solving differential equations at the output node of an inverter gives the Tpd. Depending on the input slew-rate and the load capacitance, the propagation delay time can fall in two following category [11,12]:

a) For slow input or small load capacitance:

$$T_{phl} = \frac{t_r}{V_{DD}} \left[ \sqrt{K_{log}} + V_{th} \right] - \frac{t_r}{2}$$

(2)

Where:

$$K_{\log} = \frac{1}{K_{y}} \ln \left[ \frac{0.5 V_{DD} - \frac{1}{\lambda}}{V_{DD} - \frac{1}{\lambda}} \right]$$

$$K_{y} = \frac{\beta_{s} t_{r} \lambda}{C_{L} (\alpha + 1) V_{DD}}$$

b) For fast input or large load capacitance:

$$T_{phl} = \frac{1}{K_z} \ln \left[ (0.5V_{DD} - K_2) / \left( V_{DD} - \frac{1}{\lambda} \right) \right] - \frac{t_r}{2}$$

(3)

Where:

$$K_z = \frac{\beta_s \lambda (V_{DD} - V_{th})^{\alpha}}{C_L}$$

## 3. PROPOSED ALGORITHM FOR SIMULATION OF RANDOM VARIATIONS

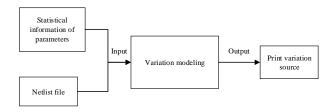

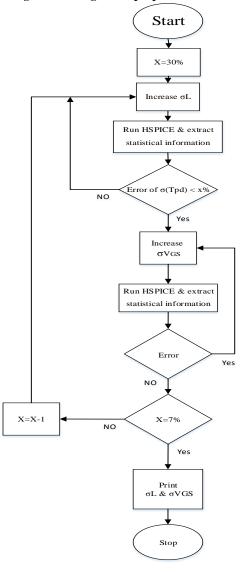

In the proposed approach, it is possible to predict the statistical behavior of one or more parameters. It means that by adding a few Gaussian voltage or current sources, the statistical behavior of important parameters can be replicated. Since two important sources of statistical variations arise from Random Dopant Fluctuations (RDF) and Line Edge Roughness (LER) [13,14], it will be physically meaningful to add one Gaussian source in series with the MOSFET gate to produce appropriate VTH variations roughly close to the amount which is produced by the impact of RDF and to incorporate L variations in HSPICE netlist close to the amount that is produced by LER. Fig.1 represents the block diagram for two important inputs and one output of the proposed algorithm. The statistical information of target parameters includes the mean and standard deviation of those parameters. The netlist file should be given to the input of the algorithm as well. Then, adding variations in the input file as shown in Fig.2, the target parameter variations are investigated using HSPICE Monte-Carlo simulation results. Parameter X represents the error introduced in the statistical simulations. Monte-Carlo HSPICE simulations are carried out for 1000 iterated simulations and the statistical behavior of target parameters are extracted.

Using just  $\sigma(L)$  will be generally insufficient to produce small error and it is observed that adding Gaussian voltage in series

with the gate  $\sigma(V_G)$  will be essential to decrease the introduced statistical error. Based on the modeling requirement, the loop will be executed in consecutive iterations until it reach the minimum assumption of X=7% or less. The output of the algorithm will be the final values for  $\sigma(L)$  and  $\sigma(V_G)$ .

Fig.1:Block diagram of proposed variation modeling.

Fig.2: Proposed Algorithm of variation modeling.

### 4. STATISTICAL MODELING OF $T_{PD}$ FOR BASIC DIGITAL BLOCKS

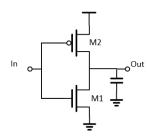

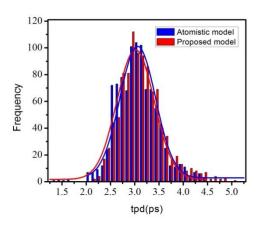

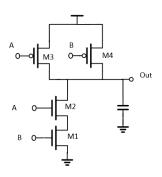

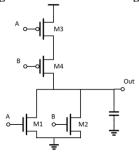

In this article, we have used atomistic simulation results as a reference of comparison to accurately evaluate the accuracy of our results. The statistical compact models arising from atomistic simulations serves as gold standard because they are calibrated against experimental results [15,16]. Fig.3 shows schematic circuit of a CMOS inverter as the most important basic digital building block. The proposed algorithm has been implemented on the inverter to replicate Tpd of the output node. The statistical input information of Tpd is derived from 'atomistic' simulations using 1000 accurate HSPICE model cards in 35nm technology nodeThe variation inputs are then calculated for the proposed algorithm as  $\sigma(L)$ =5.5nm and  $\sigma(V_G)=53mv$ . Fig. 4 depicts the comparison of Tpd histogram using both 'atomistic' model cards and the proposed algorithm. Table 1 represents the relative errors introduced in the mean and standard deviations of Tpd obtained from the proposed algorithm in respect to the corresponding values from 'atomistic' simulations. Fig. 5 and Fig.6 show the NAND2 and NOR2 gates which are used to investigate the implementation of the proposed algorithm on other basic digital building blocks. It should be noticed that in these cases, 3 different transitions of input combinations to a reference of "00" state are simulated and the errors should be acceptable in all 3 transitions.

Fig.3: Schematic of Inverter gate.

Fig.4: Histogram graph of variations of Tpd in Inverter.

The red bins are for Atomistic model and blue bins are proposed model.

Table 1.Statistical variation of Tpd for basic inverter.

| Atomistic | 4.31E-12 | 4.66E-13 |

|-----------|----------|----------|

|-----------|----------|----------|

| Proposed model | 4.25E-12 | 4.65E-13 |  |

|----------------|----------|----------|--|

| Error(%)       | 1.45     | 0.18     |  |

For NAND2 circuit, the standard deviations of  $\sigma(L)$ =4.6nm and  $\sigma(V_G)$ =50mvare used but we have introduced another Gaussian source of  $\sigma(W)$ =5nm to reduce errors to less than 7% in all of cases. The minimum error belongs to the transition from "01" to "00" state as shown in Table 2. The statistical variation of Tpd for NOR2 gate is represented in Table 3. The statistical modeling of Tpd is carried out with  $\sigma(L)$ =6nmand  $\sigma(W)$ =5nmfor this case and the maximum error is for a "11" to "00" transition. Nevertheless, the errors remain less than 7% for all transitions.

Fig.5: Schematic of NAND2 gate.

Fig.6: Schematic of NOR2 gate.

### 5. CONCLUSION

A random variability simulation algorithm has been proposed in this paper. It is based on initial assumptions for channel length variations caused by LER, and  $V_{TH}$  variations based on RDF.The promising conclusions stemmed from the accuracy of our results make a new roadmap for the future work in this field. The proposed algorithm can be extended for different channel length transistors in the state of the art technologies. Moreover, it can be used to benchmark modeling of statistical and random variability in a broad range of digital circuits. The

Table 2.Statistical variation of Tpd for NAND2.

| state             | 00       |          | 10       |          | 01       |          |

|-------------------|----------|----------|----------|----------|----------|----------|

|                   | mean     | STD      | mean     | STD      | mean     | STD      |

| Atomistic         | 6.30E-12 | 4.96E-13 | 6.77E-12 | 5.40E-13 | 8.21E-12 | 7.02E-13 |

| Proposed<br>model | 6.37E-12 | 4.64E-13 | 6.56E-12 | 5.34E-13 | 8.37E-12 | 7.45E-13 |

| Erro |  | -1.10 | 6.41 | 3.09 | 1.06 | -2.00 | -6.11 |

|------|--|-------|------|------|------|-------|-------|

|------|--|-------|------|------|------|-------|-------|

#### Table 3.Statistical variation of Tpd for NOR2.

| State             | 11       |          | 01       |          | 10       |          |

|-------------------|----------|----------|----------|----------|----------|----------|

|                   | mean     | STD      | mean     | STD      | mean     | STD      |

| Atomistic         | 6.07E-12 | 3.85E-13 | 6.04E-12 | 4.96E-13 | 8.63E-12 | 7.67E-13 |

| Proposed<br>model | 5.82E-12 | 3.60E-13 | 5.96E-12 | 5.18E-13 | 8.38E-12 | 7.49E-13 |

| Error (%)         | 4.11     | 6.37     | 1.25     | -4.44    | 2.92     | 2.33     |

main advantages of the proposed algorithm are: (i)- it can be easily extended to any target circuit with multi parameters.(ii)- it consumes much less computational resources compared with 'atomistic' simulations while the error remains less than 7% for inverter, NOR2 and NAND2 circuits.

### 6. ACKNOWLEDGMENTS

The authors would like to thank the University of Glasgow, UK for supplying statistical HSPICE librarymodelcards based on their accurate atomistic simulator, GARAND.

#### 7. REFERENCES

- [1] F. Hong, B. Cheng, S. Roy and D. Cumming, "An Analytical Mismatch Model for on coms Device under the Impact of Intrinsic Device Variability", IEEE ISCAS May, pp. 2257-2260, 2011.

- [2] G. Cijan, T. Tuma and A. Burmen, "Modeling and simulation of MOS transistor mismatch", International Conference on Proc. 6th Eurosim, 2007.

- [3] V. Wason, J. An, Jung-Suk Goo, Zhi-Yuan Wu, Qiang Chen, C. Thuruthiyil, R. Topaloglu, P. Chiney and A. Icel, "Statistical Compact Modeling and Si Verification Methodology", International Conference on Solid-State and Integrated Circuit Technology, pp.1198 – 1201, 2006.

- [4] K. Bult and A. Buchwald, "An embedded 240-mW 10-b 50-MS/s CMOS ADC in 1-mm", IEEE Journal of Solid-State Circuits, Vol. 32, pp. 1887-1895, 1997.

- [5] J. B. Shyu et al., "Random errors in MOS capacitors", IEEE Journal of Solid- State Circuits, Vol. 17, No. 6, pp. 948–955, 1982.

- [6] J. B. Shyu et al., "Random error effects in matched MOS capacitors and current sources", IEEE Journal of Solid-State Circuits, vol. 19, pp. 1070-1076, 1984.

- [7] M. Pelgrom, A.Duinmaijer and A.Welbers, "Matching properties of MOS transistors", IEEE Journal of Solid-State Circuits, Vol. 24, No. 6, pp. 1433-1989, 1989.

- [8] T. Sakurai and A. R. Newton, "Alpha-power law MOSFET model and its applications to CMOS inverter delay and other formulas," Solid-State Circuits, IEEE Journal of, vol. 25, pp. 584-594, 1990.

- [9] M. M. Mansour and A. Mehrotra, "Modified Sakurai-Newton current model and its applications to CMOS digital circuit design," in VLSI, 2003. Proceedings. IEEE Computer Society Annual Symposium on, 2003, pp. 62-69.

- [10] N. Chandra, A. Kumar Yati, and A. B. Bhattacharyya, "Extended-Sakurai-Newton MOSFET Model for Ultra-Deep-Submicrometer CMOS Digital Design," VLSI Design, 2009 22nd International Conference on, pp. 247-252, 5-9 Jan. 2009 2009.

- [11] S. Gummalla, A. R. Subramaniam, C. Yu, and C. Chakrabarti, "An analytical approach to efficient circuit variability analysis in scaled CMOS design," in Quality Electronic Design (ISQED), 2012 13th International Symposium on, 2012, pp. 641-647.

- [12] P. Liu, Y.-B.Kim, and Y. J. Lee, "An accurate analytical propagation delay model of nano CMOS circuits," in IEEE International SoC Design Conference (ISOCC), 2007, pp. 200-203.

- [13] R. Keyes, "Effect of randomness in the distribution of impurity ions on FET thresholds in integrated electronics", IEEE Journal of Solid-State Circuit, Vol. 10, No. 4, pp. 245-247, 1975.

- [14] A. Asenov, S. Kaya, and A. Brown, "Intrinsic parameter fluctuations in decananometer MOSFETS introduced by gate line edge roughness", IEEE Transactions on Electron Devices, Vol. 50, No. 5, pp. 1254-1260, 2003.

- [15] Asenov, M. Jaraiz, S. Roy, G. Roy, et al., "Integrated Atomistic. Process and Device Simulation of Decananometre MOSFETs", Proc. SISPAD2002, pp. 87-90, 2002.

- [16] Cheng, et al. "Integrating 'atomistic', intrinsic parameter fluctuations into compact model circuit analysis." European Solid-State Device Research, ESSDERC'03. 33rd Conference on IEEE, 2003.

IJCA™: www.ijcaonline.org 40