# **Review of Quaternary Adders in Voltage Mode**

# **Multi-Valued Logic**

Neha W. Umredkar

P.G. Department of Electronics Engg B. D. College of Engineering, Sevagram. B. D. College of Engineering, Sevagram.

M.A.Gaikwad, Ph.D Profesor Dean R&D and H.O.D. E&T Dept.

D.R.Dandekar P.G. Electronics Dept. B.D.College of Engg. Wardha

# ABSTRACT

The Binary logic circuits design is limited by the requirement of number of interconnections which increases the chip area with increase in logic. Multi valued logic designs are gaining importance form that perspective. Adders are one of the important part of the processing element and hence it has a focus of research. Therefore design of adders using multi valued logic can prove to be very useful. Thus there is a need to design a optimal adder. In this paper we review Quaternary Adders circuit. The proposed adders are to be design in Multi-Valued Voltage Mode Logic and investigate the effect of one parameter on another. Optimized adders will be designed, analyzed and proposed for multi-valued logic arithmetic unit design which will achieve the practical ranges of parameters of circuit.

## Keywords

Voltage Mode Multiple-Valued Logic, Quaternary Logic.

# **1. INTRODUCTION**

Computers have become very complex machines, running on processors with millions and millions of circuits and running at clock speeds of 4GHz and higher. The programs running on these machines are even more complex, involving millions of instructions. Despite all this complexity, the stunning fact is that the basic component of all this machinery is the very basic binary switch, which switches between two states. Some people have tried to explain all this complexity from a perspective of "symbol processing." Other has tried to connect our thinking with binary logic, which is the 'language' of binary switching. No matter how it is all explained, the fact remains, that for over 70 years, computing devices as we know them have been based on the simplest of simple switching states: "on" and "off". Binary technology appears to be a given, a fundamental approach to allow a machine to perform instructions. It also appears to be limiting. Just two states? To automate all our thought processes? What would one be able to do with a machine that performs non-binary switching? What would it require? What would it look like? How does one apply it?

The answer to this is Multi-valued logic. "Elean Dubrova" basically defines Multi-valued logic is like painting a picture having all possible colours available [1]. Multi-value logic is defined as a non-binary logic and involves the switching between more than two states. Multi-valued logic means instead of assuming one of the two states as per in binary logic, signal may assume one of more than two states, for instant 4 states. Binary values take only values {0,1}.Multivalued synthesis take multivalued variables Xi can take values  $Pi=\{0,...,pi-1\}.$

Multi-valued logic offers important advantage like more information can be processed over a given set of lines to reduce the burden of interconnections and thereby switching[2]. The

advantage of Multi-valued logic are the use of fewer operations potentially fewer gates and reduction in number of interconnections and switching. The reduction of dynamic power dissipation is VLSI applications is the major challenge for today's engineers as major portion of the power is consumed by interconnect and switching [3].

Adders form the basic part of processing element. An adder is basically a circuit which is used in variety of applications. So, if we create an optimized adder simultaneously the processing elements will be improved. This will fasten the calculation of arithmetic Logic Unit which further improves and fasten the performance of the unit. Using an optimized adder using Multi-Valued logic will lessen the space required. Optimized adders will prove to be useful in other Digital Signal Processing as adders are the basic part of Digital Signal Processing.

Increased data density, reduced dynamic power dissipation, and increased computational ability are among some of the key benefits of Multiple Valued Logic (MVL). Several Implementation methods have been proposed in the recent papers to realize the Multi-valued logic circuits.[4,5]. They can be fundamentally categorized as current -Mode, voltage mode and mixed mode circuits. Several prototype chips of currentmode CMOS circuits have been fabricated, showing somewhat better performances compared to the corresponding binary circuit[6-9]. Even though current-mode circuits have been popular and offer several CMOS binary logic circuits from the perspective of dynamic switching activity. Several approaches for quaternary circuit design have been proposed [7-12], in voltage mode technique. benefits, the power consumption is high due to their inherent nature of constant current flow during the operation. Alternatively, voltage-mode circuits consume a large majority of power only during the logic level switching.

Hence, voltage-mode circuits do offer lesser power consumption which has been the key benefit of traditional CMOS binary logic circuits from the perspective of dynamic switching activity. Several approaches for quaternary circuit design have been proposed [7-12], in voltage mode technique. In current mode circuits the power dissipation is high due to their inherent nature of constant current flow during the operation. Alternatively, volatage mode circuits consume a large majority of power only during the logic level switching. Hence, voltage -mode circuits offers lesser power consumption which is the key benefit. Quaternary logic (radix-4-valued) is chosen as the base radix. Using a quaternary radix offers all the benefits of MVL with the important advantage of being able to easily interface with traditional binary logic circuits.

# 2. Review of MVL Adders

Novel quaternary half adder, full adder, and a carry-look ahead adder were introduced by M Thoidis [13]. In his paper, the proposed circuits were static and operate in voltage mode.

They reported no static power dissipation as the circuits were static in nature.

Ricardo designed a new truly full adder quaternary circuit using 3 power supply lines and multi-Vt transistors. He has designed quaternary multiplexer (MUX) 4:1 with 4 quaternary inputs and one quaternary output and used this MUX as a building block to construct full adder. The proposed multiplexer circuit is based on voltage-mode quaternary logic CMOS circuits. These circuits use several different transistors with different threshold voltages and operate with four voltage levels, corresponding to 0V common terminal and three power supply lines of 1V, 2V and 3V. The quaternary MUX is designed using Down Literal Circuits (DLCs), binary inverters and pass transistor gates. Down Literal Circuits performs the functions shown in table I. There are 3 possible Down Literal Circuits in quaternary logic, named DLC1, DLC2 and DLC3.

| IN | Down Literal Circuit Output |      |      |  |  |  |  |  |  |

|----|-----------------------------|------|------|--|--|--|--|--|--|

| IN | DLC1                        | DLC2 | DLC3 |  |  |  |  |  |  |

| 0  | 3                           | 3    | 3    |  |  |  |  |  |  |

| 1  | 0                           | 3    | 3    |  |  |  |  |  |  |

| 2  | 0                           | 0    | 3    |  |  |  |  |  |  |

| 3  | 0                           | 0    | 0    |  |  |  |  |  |  |

Table I. Down Literal Circuit Truth Table

The Down Literal Circuits are designed in CMOS technology with 3 different threshold voltages for PMOS transistors and 3 different threshold voltages for NMOS transistors. Table II shows Vt values relative to the transistors source-bulk voltages.

|     | T1                                          | T2  | T3   | T4  | Т5   | T6  |  |  |  |

|-----|---------------------------------------------|-----|------|-----|------|-----|--|--|--|

| Vt  | -2.2                                        | 2.2 | -1.2 | 0.2 | -0.2 | 1.2 |  |  |  |

| Тур | PMO                                         | NMO | PMO  | NMO | PMO  | NMO |  |  |  |

| e   | S                                           | S   | S    | S   | S    | S   |  |  |  |

|     | Table II Transistor Vt values related to Vs |     |      |     |      |     |  |  |  |

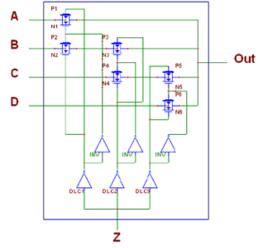

The quaternary multiplexer 4:1 is designed using the 3 DLCs, 3 binary inverters and 6 pairs of pass transistor gates and its schematic is presented in figure 1.

Figure 1 : Quaternary MUX 4:1 schematic circuit

This circuit has 4 quaternary inputs (A, B, C and D), one quaternary output (Out) and 1 quaternary control signal (Z) that sets the output to one of the 4 inputs.

Proposed technique benefits large scale circuits since the much power dissipation with increased speed can lead to the development of extremely low energy circuits while sustaining the high performance required for many applications [14].

Ouaternary full adders based on output generator sharing are proposed by Hirokatsu . Full adder are proposed for a highperformance multi-processor which consists of many processing elements (PEs). Arbitrary quaternary functions are represented by the combination of input-value conversion and several quaternary output generations. The use of appropriate input-value conversion makes it possible to reduce the number of output generators, which improves the performance of the resulting Quaternary full adders. In this paper the Quaternary full adder is constructed using the above method and their efficiencies are demonstrated in terms of delay and power dissipation in comparison with those of a corresponding binary CMOS implementation. Table III shows truth tables of quaternary to binary conversion.

| IN | G0.5 | G1.5 | G2.5 | IN | GA | G |

|----|------|------|------|----|----|---|

| 0  | 0    | 0    | 0    | 0  | 0  | 0 |

| 1  | 1    | 1    | 0    | 1  | 1  | 0 |

| 2  | 1    | 1    | 0    | 2  | 1  | 1 |

| 3  | 1    | 1    | 1    | 3  | 0  | 1 |

| a) |      |      |      | ŀ  | )  |   |

Table III Truth tables of quaternary to binary conversion represented by

a) Three kinds of binary signals b) two kinds of binary signals In a basic quaternary circuit, each comparator has one logical threshold  $T(T=\{0.5,1.5,2.5\}$  and each quaternary input signal is converted into three binary signalsG0.5,G1.5 and G2.5, given in Eqs.(1)-(3) as

$$G0.5 = 0$$

if IN < 0.5,

1 if IN > 0.5 (1)

$$G1.5 = 0$$

if  $IN < 1.5$ ,

1 if  $IN > 1.5$  (2)

$$G2.5 = 0 \quad \text{if } IN < 2.5, \\ 1 \quad \text{if } IN > 2.5 \tag{3}$$

By allowing a comparator to have two logical thresholds, these signals can be represented in two signals GA and GB given in Eqs.(4)-(5) as

$$GA = 0 \text{ if } IN < 0.5 \text{ or } 2.5 < IN 1 \text{ if } 0.5 < IN < 2.5$$

(4)

$$GB = 0 \quad \text{if IN} < 1.5, \\ 1 \quad \text{if IN} > 1.5$$

(5)

This representation enables to reduce comparators, which results in the reduction of storage elements in quaternary sequential circuits. Table 4 shows truth tables of quaternary full addition.

Table IVTruth tables of quaternary Full addition.Sum Block:

| <b>S</b> 0 |   |   | 2 | x |   | SI | S1 |   | Х |   |   |  |

|------------|---|---|---|---|---|----|----|---|---|---|---|--|

|            |   | 0 | 1 | 2 | 3 |    |    | 0 | 1 | 2 | 3 |  |

|            | 0 | 0 | 1 | 2 | 3 |    | 0  | 1 | 2 | 3 | 0 |  |

|            | 1 | 1 | 2 | 3 | 0 |    | 1  | 2 | 3 | 0 | 1 |  |

| Y          | 2 | 2 | 3 | 0 | 1 | Y  | 2  | 3 | 0 | 1 | 2 |  |

|            | 3 | 3 | 0 | 1 | 2 |    | 3  | 0 | 1 | 2 | 3 |  |

Carry block:

X and Y are the adder inputs,S0 and CO0 are the sum and carry outputs when the carry input is "0", and S1 and CO1 are the sum and carry outputs is "1".The expressions for S0, S1, CO0 and CO1 are given in Eqs.(6)-(9) as

$$S0 = X+Y \text{ if } X+Y < 4 X+Y-4 \text{ if } X+Y>=4$$

(6)

$$S1 = X+Y+1 \text{ if } X+Y+1 < 4$$

(X+Y+1)-4 if X+Y+1 >=4 (7)

$$CO0 = 0 \text{ if } X+Y<4 \\ 1 \text{ if } X+Y>=4$$

(8)

$$CO1 = 0 \text{ if } X+Y+1<4 \\ 1 \text{ if } X+Y+1>=4$$

(9)

If Y'is defined as the sum of Y and CI,S0 and S1(CO0 and CO1)are naturally summarized in S(CO0) for which expressions correspond to those of quaternary half addition, given in Eqs. (10) and (11) as

$$S = X+Y'$$

if  $X+Y' < 4$  (10)

X+Y'-4 if X+Y'>=4

$$CO = 0 \text{ if } X+Y'<4 \\ 1 \text{ if } X+Y'>=4$$

(11)

This means that quaternary full addition can be decomposed into carry pre-addition and quaternary half addition. The algorithm of decomposed quaternary full addition is summarized as

> Step 1 : Y' = Y+C1 if Y+C1 < 4 Y+C1-4 if Y+C1=4, Step 2(a) : S = X+Y' if X+Y'<4 X+Y'-4 if X+Y'>=4Step2(b) : CO = 0 if X+Y'<4 1 if X+Y'>=4 OR Y+C1=4

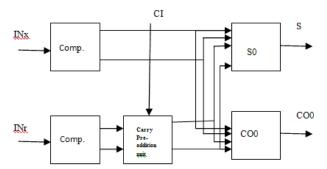

Figure 2 : Proposed quaternary full adder

| CO | C00 |   | 2 | x |   | CO1 |   | Х |   |   |   |

|----|-----|---|---|---|---|-----|---|---|---|---|---|

|    |     | 0 | 1 | 2 | 3 |     |   | 0 | 1 | 2 | 3 |

|    | 0   | 0 | 0 | 0 | 0 |     | 0 | 0 | 0 | 0 | 0 |

|    | 1   | 0 | 0 | 0 | 1 |     | 1 | 0 | 0 | 1 | 1 |

| Y  | 2   | 0 | 0 | 1 | 1 | Y   | 2 | 0 | 1 | 1 | 1 |

|    | 3   | 0 | 1 | 1 | 1 |     | 3 | 1 | 1 | 1 | 1 |

Figure 2 shows a block diagram of the proposed quaternary full adder. The decomposition of the quaternary full addition into carry pre-addition and quaternary half addition enables to share the S0 generator and S1 generator (the C0 generator and C1 generator) Since the output generators have large input capacitances, the sharing results in high-speed operation.

| Logic value | 0 | 1   | 2   | 3   |

|-------------|---|-----|-----|-----|

| Voltages[V] | 0 | 0.4 | 0.9 | 1.2 |

Figure 3 : Relation between MV Logic values and voltage values in voltage mode implementation.

Figure 3 indicates logical values and threshold values, and their corresponding voltage values, respectively. The proposed adders are designed with reduction in delay and power[15].

The implementation of Quaternary Signed Digit addition was presented in paper [16]. The test confirms the superior performance of the QSD adder implementation over other adders due to the carry - free addition scheme. The complexity of the QSD adder was linearly proportional to the number of digits, which are of the same order as the simplest adder, the ripple carry adder. This QSD adder can be used as a building block for other arithmetic operations such as multiplication, division, square root, etc. With the QSD addition scheme, some well-known arithmetic algorithms can be directly implemented [16].

Supplementary Symmetrical Logic Circuit (referred as SUSLOC) was presented in [17]. This work illustrates how quaternary gates can be implemented using the SUSLOC circuit structure. These gates were then used to build three different addition circuit architectures: carry-ripple, carry-look ahead, and carry-select. These three quaternary addition circuits are then modeled using the System Verilog language. The three different adder architectures are designed and compared for area and estimated performance with their binary circuit counterparts

[17].

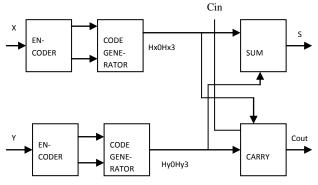

Full adder circuit proposed by Vasundara Patel K.S., K.S. Gurumurthy is based on Encoder, code generator, sum block and carry block. Encoder is required for the conversion shown in table 4, consists of DLC1 and DLC3 (Down literal circuit) [18].

A full adder circuit is designed by converting the quaternary logic in to unique code, which enables to implement circuit with reduced hard ware. Sum and carry are processed in two separate blocks, controlled by code generator unit. Simple pass transistors are used for implementation. The design is targeted for the 0.18  $\mu$ m CMOS technology. Area of the designed circuits is less than the corresponding binary circuits and quaternary adders because number of transistors used are less. Figure 4 Shows the block diagram of proposed adder.[19]

#### Figure 4 : Proposed quaternary full adder

This proposed adder consists of Encoder block, Code Generator block Sum and Carry blocks.

In the adder proposed by Takahiro Hanyu a high-speed, lowpower and compact processing element using quaternary differential logic is proposed for a multi-core singleinstruction multiple-data (SIMD) processor. A two-bit addition which is the critical path of the ALU is attributed to a one-digit quaternary addition that is directly performed by using multiple-valued current- mode (MVCM) differential logic circuitry. A one-digit quaternary flip-flop is also simply implemented by using the MVCM differential logic circuitry. [20]

### **3. PROPOSED ADDERS**

Taking in view the investigation which includes three quaternary full adder circuits, proposed by Recardo Cuna et.al [17],Hirokatsu Shirahama et.al [18], Hirokatsu Shirahama et.al

[21] and corresponding binary adder. In paper [17] 180nm technology file and power supply of 3V is used. It is

dissipating dynamic power supply of 181  $\mu$ W at 250 MHz and it shows delay of 2.24ns. It requires 332 transistors. Paper [18] uses 90nm technology files and 1.2V power supply. Propagation delay of 113ps and dynamic power 55  $\mu$ W at 1 GHz is observed.. In [21] 180nm and 1.8V power supply is used. Propagation delay of 1.4ns and power dissipation of 194  $\mu$ W is observed at 300MHz. In the adder proposed by Takahiro Hanyu used 180 nm technology, 3 V power supply and 250 M Hz on synopsys Hspice and Cscope for full adder design and 1GHz for half adder design. Logic levels are well defined and independent of fabrication process variations of the component[21]. Power dissipation and delay are observed for sum and carry blocks of both half adder and full adder. Proposed half adder dissipates 112  $\mu$ W of power at 1 GHz and shows delay of 1.8 ns. Number of transistors required are 76. Proposed full adder dissipates 84  $\mu$ W of power at 250 MHz and delay of 2.02 ns and number of transistors required are 148. The use of appropriate input value conversion makes it possible to reduce the hardware.

Proposed adders are to be implemented in voltage mode using Quaternary logic. Thus an optimal adder is to be design by investigate the effect of one parameter on another.

## 4. RESULT AND DISCUSSION

Taking in view the discussion and the design of different quaternary adders an optimal Quaternary adder is to be designed, analyzed and proposed for multi-valued logic arithmetic unit design which will achieve the practical ranges of parameters of circuit. Consequently, this design is appropriate to be applied for high performance which consists of many processing elements.

## 5. CONCLUSION

Different quaternary adders are designed analyzed and proposed. These quaternary adders are designed using different techniques and different adders are compared on basis of different parameters. Thus we investigate ,analyze different adder on the basis of different parameters. Hence, we can create an optimized adder and can investigate the effect of one parameter on other.

### 6. REFERENCES

- [1]Elean Dubrova, "Multiple-Valued Logic in VLSI: Challenges and Opportunities" Computer 21,4,(1988),28-42

- [2] T.Hlguchl and M.Kameyama," Synthesis of multiplevalued logic networks based on tree type universal logic modules", Proc. Of 5<sup>th</sup> Int. Symponisum on multiplevalued logic, Bloomington ,pp.121-130.

- [3] Scott Hauck, "Asynchronous design Methodologies: An Overview", Proceedings of the IEEE. Vol.83

- [4] S. Hurst, "Multiple-valued logic -its status and its future", IEEE trans.On Computers. Vol. C-33, no.12, pp. 1160-1179, 1984.

- [5] M. Kameyama, "Toward the Age of Beyond-Binary Electronics and Systems", Proc. of IEEE Int. Symp. On Multiple-Valued Logic, 1990.

- [6] Hanyu, M. Kameyama, "A 200 MHz pipelined multiplier using 1.5V-supply multiple valued MOS current-mode circuits with dual-rail source-coupled logic", IEEE Journal of Solid-State Circuits vol.30, no.11, pp.1239-1245, 1995.

- [7] B. Radanovic, M. Syrzycki, "Current-mode CMOS adders using multiple-valued logic", Canadian Conference on Electrical and Computer Engineering, pp.190-193, 1996.

- [8] J. Shen et al., "Neuron-MOS current mirror circuit and its application to multi-valued logic", IEICE Trans. Inf. & Syst. E82-D,5 pp.940-948, 1999.

- [9] D. H. Y. Teng, R. J. Bolton, "A self-restored currentmode CMOS multiple-valued logic design architecture", 1999 IEEE pacific Rim Conf. on Communications, Computers Signal Processing (PASRIM'99), pp. 436-439,1999.

- [10] F. Wakui and M. Tanaka, "Comparison of Binary Full Adder and Quaternary Signed-Digit Full Adder using High- Speed ECL", International Symposium on Multiple Valued Logic, pp. 346-355,1989.

- [11] M.K. Habib and A.K. Cherri, "Parallel Quaternary Signed- Digit Arithmetic Operations: Addition, Subtraction, Multiplication, and Division", Journal of Optics and Laser Technology, vol. 30, pp.515-525. 1998.

- [12] Kawahito, S. Kameyama, "A 32 X 32 bit Multiplier using Multiple-valued MOS Current Mode Circuit", Journal of Solid-State Circuits, IEEE, vol.1, pp.124 -132, 1988.

- [13] R.G. Cunha, H. Boudinov, and L. Carro, A Novel Voltage- Mode CMOS Quaternary Logic Design, IEEE Trans. On ElectronicDevices, 53(6) (2006)1480-1483.[14] Y. Yasuda, Y. Tokuda, S. Zhaima, K. Pak, T. Nakamura, A.Yoshida, "Realization of quaternary logic circuits by N- Channel MOS Devices", IEEE Journal of Solid State Circuits, vol.21, no.1, pp.162-168, 1986.

- [15] Yuichi Baba, "Multiple-Valued Constant-Power Adder for Cryptographic Processors" 39th International Symposium On Multiple-Valued Logic IEEE, 2009

- [16] M. Thoidis , D. Soudris , J.-M. Fernandez, and A. hanailakis, "The circuit design of multiple-valued logic voltage-mode adder", Proceedings of the 2001 IEEE International Symposium on Circuits and Systems (ISCAS 2001), Sydney, Australia, pp. 162-165 May 6-9, 2001.

- [17] Ricardo Cunha, "quaternary lookup tables using voltage mode CMOS logic design", ISMVL 2007, 37th International Symposium on Multiple-Valued Logic, pp.56- 56, 2007, 13-16 May, 2007.

- [18] Hirokatsu Shirahama and Takahiro Hanyu, "Design of High-Performance Quaternary Adders Based on Output-

Generator Sharing", Proceedings of the 38th International Symposium on Multiple Valued Logic, pp. 8-13. 2008.

- [19] Dakhole P. K., Wakde D. G. "Multi-Digit Quaternary Adder on Programmable Device : Design & Verification", International Conference on Electronic Design, Penang, Malaysia, December 1-3, 2008.

- [20] Satyendra R. Datla et.al, "Quaternary Addition Circuits Based on SUSLOC Voltage-Mode Cells and Modeling with System Verilog", 39th International Symposium on Multiple-Valued Logic, IEEE, 2009.

- [21] Vasundara Patel K.S., K.S. Gurumurthy, "Multi-valued Logic Addition and Multiplication in Galois Field", International Conference on Advances in Computing, Control, and Telecommunication Technologies pp. 752-755, December 2009.

- [22] Vasundara Patel K.S.,K.S. Gurumurthy, "Design of High Performance Quaternary Adders" 2011 IEEE International Conference on Multiple-Valued Logic.

- [23] Hirokatsu Shirahama and Takahiro Hanyu et.al, "Design of a Processing Element Based on Quaternary Differential Logic for a Multi-Core SIMD Processor", 2007 International Symposium on Multiple-Valued Logic.

- [24] Hirokatsu Shirahama and Takahiro Hanyu et.al, "Design of a Processing Element Based on Quaternary Differential Logic for a Multi-Core SIMD Processor", ISMVL, Proceedings of the 37<sup>th</sup> International Symposium on Multiple-Valued Logic, pp. 43, 2007.