# Energy-Efficient CMOS Full Adder for Arithmetic Applications

Kiran Barapatre

IV sem M.Tech.(VLSI)

Priyadarshini College of

Engineering, Nagpur.

P.J.Suryawanshi

Electronics Dept.

Priyadarshini College of

Engineering, Nagpur

Sanket Lichade IV sem M.Tech. (VLSI) Priyadarshini College of Engineering, Nagpur.

#### **ABSTRACT**

In this paper, we present Energy efficient CMOS full adder, which is one of the basic building blocks of a modern electronic systems design. Energy-Efficiency is one of the most required features in digital electronic systems for high-performance and/or portable applications which signify PDP, it measures the energy consumed per switching event. This paper shows that complementary CMOS is the logic style of choice for the implementation of combinational circuits, if low voltage, low power, and small power-delay products are of concern with relatively low area.

## Keywords-

Adders, CMOS Full Adder, Low power, VLSI, High-Speed, Low-area.

#### 1. INTRODUCTION

In the today's world of VLSI system such as application specific DSP architectures, microprocessors, FIR filter and systolic array design there is requirement of fundamental operations such as addition. ThusFull adders are the core of many arithmetic operations such as addition, subtraction, multiplication, division and address generation. In the majority of systems, the adder is part of the critical path that determines the overall performance of the system. As stated, the system's overall performance would affected by PDP exhibited by the full-adder [1]. Hence enhancing the performance of the full adder cell results of great interest [1]. By considering this facts the design of a full-adder having low-power consumption and low propagation delay results of great interest for the implementation of modern digital systems

In advancement of mobile product, which worked with a high throughput capability makes the design of low-power adder module another significant goal to be achieved. Power dissipation can be cause by three major components in complementary metal oxide semiconductor (CMOS) circuits [2] namely switching power, short circuit power and static power. Reducing any of these components will accounts for lower power consumption for the whole system design.

## 2. PREVIOUS WORK

Various papers have been published related to the design of low power full adders. They were trying on both, the logic style and the logic structure used to build the adder. Since the standard CMOS realization [3], various full adders were built upon different static logic styles. They have been presented, namely: Differential Cascode Voltage Switch (DCVS) [4], Complementary Pass- Transistor Logic (CPL) [5], Double Pass-

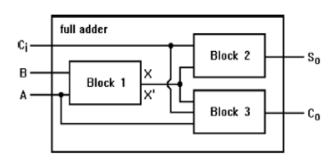

Transistor Logic (DPL) [6], and Swing Restored CPL (SR-CPL) [7]. Depending On these logic styles, few tasks have been done to build advance full adders by changing the internal logic structure of the adder module. In recent work [8], a full adder is designed by using transmission function theory. It is formed by three main logic blocks namely XOR-XNOR gate to obtain A XOR B and A XNOR B signals (Block 1), and a multiplexers to obtain the SUM (So) and CARRY (Co) outputs (Blocks 2 and 3) respectively , as shown in Figure 1.

Fig 1: Full-adder cell using three main logical blocks.

The specified logic structure is based on the full adder's truthtable shown in Table 1, and it has been accepted as the standard internal structure in the most of the field area developed for the single bit full adder cell.

Table 1- True-table for a 1-bit full adder with A, B and C as an inputs, and So and Co are outputs.

| С | В | Α | So | Со |

|---|---|---|----|----|

| 0 | 0 | 0 | 0  | 0  |

| 0 | 0 | 1 | 1  | 0  |

| 0 | 1 | 0 | 1  | 0  |

| 0 | 1 | 1 | 0  | 1  |

| 1 | 0 | 0 | 1  | 0  |

| 1 | 0 | 1 | 0  | 1  |

| 1 | 1 | 0 | 0  | 1  |

| 1 | 1 | 1 | 1  | 1  |

In paper [9], detail study is done on one bit cmos full adder, the efficient realization for block 1 in fig 1 was implemented with SR-CPL logic style. But there is an important conclusion was pointed out regards of propagation delay. For a full adder built upon the logic structure shown in Figure 1. It is essential to

obtain A XOR B and A XNOR B internal signals, which are then feed to drive other blocks which are block1 and block 2 in order to generate the final outputs. Thus the overall power consumption, depend on the delay and voltage swing of the (A XOR B) and (A XNOR B) signals, generated within the module.

Thus, to increase the operational speed of the full adder, it is essential to research for a advance logic structure that avoids the generation of internal signals used to control the selection or transmission of other signals located on the critical path.

#### 3. ENERGY EFFICIENT FULL ADDER

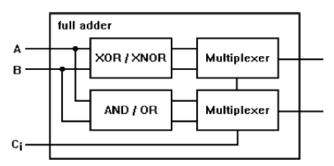

After studying the truth table of full adder in Table 1, it can be observed that the So output is equal to the (A XOR B) value when C=0, and equal to (A XNOR B) when C=1. From this observation we conclude that a multiplexer will be used to obtain the respective value based upon the Carry input, as stated earlier. Using the same scenario, the Co output is equal to the (A AND B) value when C=0, and (A OR B) value when C=1. In the similar way, carry will be used to drive a multiplexer. Hence, an energy efficient logic scheme to design a full adder cell can be formed by a logic block to get the (AXOR B) and (AXOR B) signals, other block to obtain (A AND B) and (A OR B) signals, and two multiplexers being driven by the Carry input to generate the So and Co outputs, as shown in Figure 2.

Fig 2: Alternative logic scheme for Energy Efficient Full Adder

The features and advantages that can be expected for this energy efficient logic structure are given below [10],

I. There is no requirement of internal signal for controlling the select line of multiplexers. Instead, the Carry input signal, which has full voltage swing and without delay, is used to drive the select line of multiplexers, which reduces the overall propagation delay of full adder.

II. It reduces the capacitive load for the carry input, because it is connected only to some transistor gates and not to some drain or source terminals, where the diffusion capacitance is becoming very large. Hence, the overall delay for larger modules where the carry signal falls on the critical path can be reduced.

III. The propagation delay can be tuned up individually by adjusting the XOR/XNOR and the AND/OR gates for the So and Co outputs; this criteria is advantageous for applications where the skew between arriving signals is critical for a proper operation (e.g., wave pipelining).

IV. By interchanging the XOR/XNOR signals, and the AND/OR gates to NAND/NOR gates at the input of the multiplexers, the placement of buffers at the full-adder outputs can be implemented which can improve the performance for load-sensitive applications.

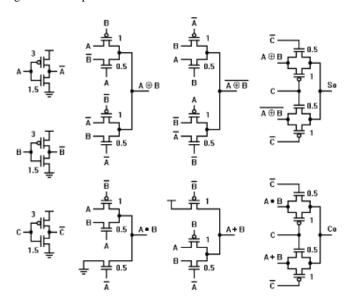

Depending on the results obtained in [11], two new full-adders will be been designed using the logic styles DPL and SR-CPL. Fig. 3 presents a full-adder designed using a DPL logic style to build the XOR/XNOR gates, and a pass-transistor based multiplexer to obtain the So output.

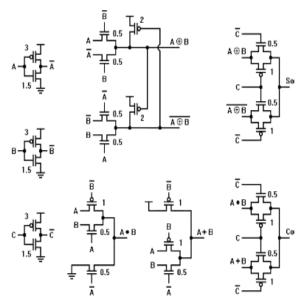

In Fig. 4 presents the SR-CPL logic Style which will be used to build XOR/XNOR gates. AND/OR gates have been built using a powerless and groundless pass-transistor configuration, respectively in both cases and a pass-transistor based multiplexer to get the Co output.

Fig 3: Full-adder designed with the Energy Efficient structure using a DPL logic style

Fig 4: Full-adder designed with the Energy Efficient structure using a SR-CPL logic style

# 4. COMPARISON OF DIFFERENT LOGIC STYLE

The logic style used in logic gates basically depends on the speed, size, power dissipation, and the wiring complexity of a

circuit. Depending on these criteria comparison of different logic style is listed below [12]

Table 2- Qualitative Logic Style Comparisons

| logic | # MOS    | output  | I/O      | swing   | #      | robust- |

|-------|----------|---------|----------|---------|--------|---------|

| style | networks | driving | decoupl. | restor. | rails  | ness    |

| CMOS  | n+p      | medgood | yes      | no      | single | high    |

| CPL   | 2n       | good    | yes      | yes     | dual   | medium  |

| SRPL  | 2n       | poor    | no       | yes     | dual   | low     |

| DPL   | 2n + 2p  | good    | yes      | no      | dual   | high    |

| LEAP  | n        | good    | yes      | yes     | single | medium  |

| EEPL  | 2n       | good    | yes      | yes     | dual   | medium  |

| PPL   | n + p    | poor    | no       | yes     | dual   | low     |

#### 5. CONCLUSION

The design of high-speed low-power full adder cells based upon an alternative logic approach has been presented. Which results in a great improvement on regards of power-delay metric for the proposed adders, when compared with several previously published realizations.

The full adders designed using improved logic structure and DPL and SR-CPL logic styles, less delay of around 720ps and less power consumption of around 840  $\mu W,$  for an overall reduction of 30% respect to the best featured one of the other adders been compared, but in general about 50% respect to the other ones.

In the future some work can be done for the designing of high-speed low-power full adders, considering alternative logic structure and trying on new realizations for the constituent logic blocks (XOR/XNOR, AND, OR and MUX cells).

# 6. REFERENCES

A. M. Shams and M. Bayoumi, "Performance evaluation of 1-bit CMOS adder cells", IEEE ISCAS, Orlando, Florida, May 1999, pp. I27 -130.

- [2] A.P.Chandrakasan, S.Sheng and R.W.Brodersen, "Lowpower CMOS digital design", IEEE JSSC, Vol. 27, April 1992, pp. 473-483.

- [3] N. Weste and K. Eshraghian, Principles of CMOS design, A system perspective, Addison-Wesley, 1988.

- [4] K. M. Chu and D. Pulfrey, "A comparison of CMOS circuit techniques: Differential cascode voltage switch logic versus conventional logic, "IEEE J. Solid-State Circuits, vol. SC-22, no. 4, pp.528–532, Aug.1987.

- [5] K. Yano, K. Yano, T. Yamanaka, T. Nishida, M. Saito, K. Shimohigashi, and A. Shimizu, "A 3.8 ns CMOS 16□16-b multiplier using complementary pass-transistor logic," *IEEE J. Solid-State Circuits*, vol. 25, no. 2, pp. 388–395, Apr. 1990.

- [6] M. Suzuki, M. Suzuki, N. Ohkubo, T. Shinbo, T. Yamanaka, A.Shimizu, K. Sasaki, and Y. Nakagome, "A 1.5 ns 32-b CMOS ALU in double pass-transistor logic," IEEE J. Solid-State Circuits, vol. 28, no. 11, pp. 1145–1150, Nov. 1993.

- [7] R. Zimmerman and W. Fichtner, "Low-power logic styles: CMOS Versus pass-transistor logic," IEEE J. Solid-State Circuits, vol. 32, no. 7, pp. 1079–1090, Jul. 1997.

- [8] N. Zhuang and H. Wu, "A new design ofthe CMOSfull adder", IEEE JSSC, Vol. 27, No. 5, May 1992, pp. 840-844

- [9] A. M. Shams and M. Bayoumi, "A new cellfor low power adders", Proceedings of the International MWSCAS, 1995.

- [10] C. Chang, J. Gu, and M. Zhang, "A reviewof 0.18-□mfull adder performances for tree structured arithmetic circuits," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 13, no. 6, pp. 686–695, Jun. 2005.

- [11] M. Aguirre and M. Linares, "An alternative logic approach to implement high-speed low-power full adder cells," in Proc. SBCCI, Florianopolis, Brazil, Sep. 2005, pp. 166– 171.

- [12] Reto Zimmermann and Wolfgang Fichtner, Fellow, IEEE" Low-Power Logic Styles: CMOS Versus Pass-Transistor Logic" in IEEE Journal Of Solid-State Circuits, Vol. 32, No. 7, July 1997.